Cheese

795 posts

Cheese

@System360Cheese

George Cozma | Editor in Chief of Chips and Cheese All opinions are my own

Bloomberg interview with Nvidia CEO Jensen Huang, on the Vera CPU Plan: "For the very first time, we're going to be offering Vera CPUs. Vera is such an incredible CPU. We're going to offer Vera CPUs as a standalone part of the infrastructure. And so not only, not only can you run your computing stack on NVIDIA GPUs, you can now also run your computing stack, wherever their CPU workload, run on Nvidia CPUs... ""Vera is completely revolutionary...Coreweave is going to have to race if Coreweave's going to be the first to stand up Vera CPUs. We haven't announced any of our CPU design wins, but there are going to be many."

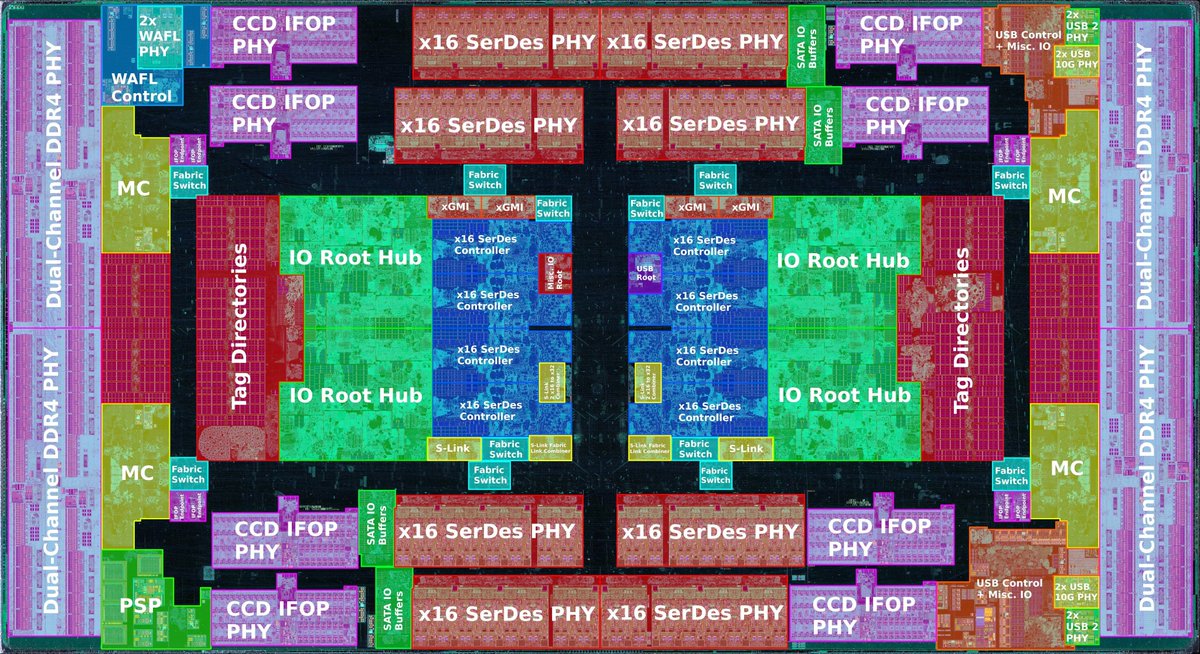

Some initial assumptions about @AMD's upcoming Zen 6 Venice server CPU👇

👀

In defense of NOT using salt, I have to say that it really does destroy things—from plants to even cars. The roads in Ithaca, NY are salted so excessively in the winter that everyone who lives there knows you have to wash your car DAILY in winter (with an undercarriage cleaning) to prevent the whole bottom of your car from rusting away.

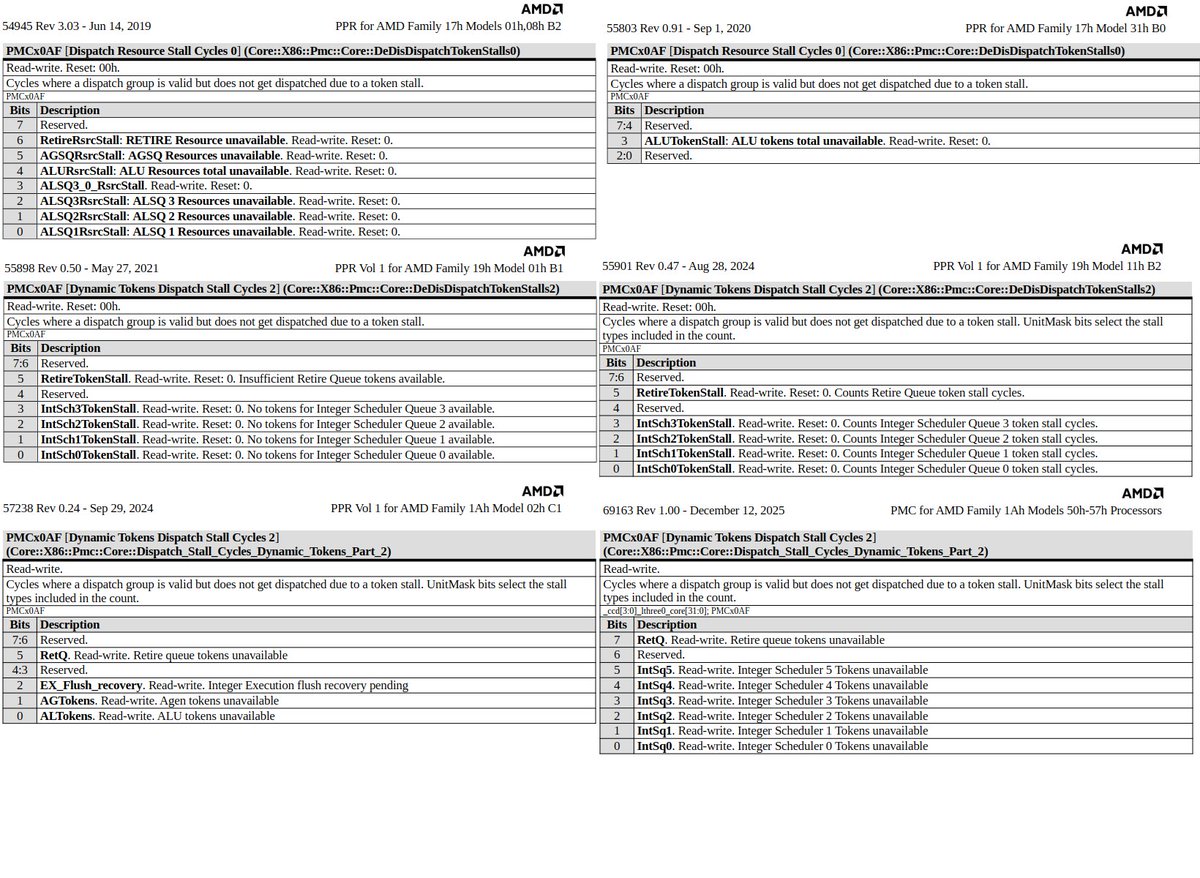

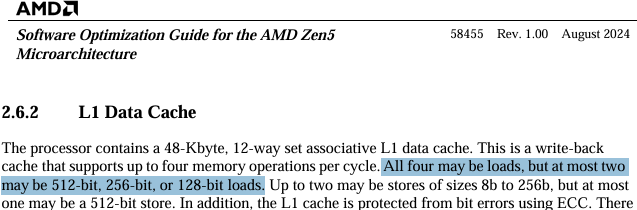

#AMD released the first official #Zen6 doc: "Performance Monitor Counters for AMD Family 1Ah Model 50h-57h Processors" 69163 v1.00 docs.amd.com/v/u/en-US/6916… Confirmed features: PMCx003: #FP16 PMCx2C0: #MemoryProfiler PMCx0AF: 6 Integer Scheduler (vs 1 central of #Zen5)

@bertverrycken CPO

“I think they’re getting clean rooms wrong in these modern (chip) fabs. I’m going to make a bet here, that @Tesla will have a 2nm fab, and I can eat a cheeseburger and smoke a cigar in the fab.”