Sabitlenmiş Tweet

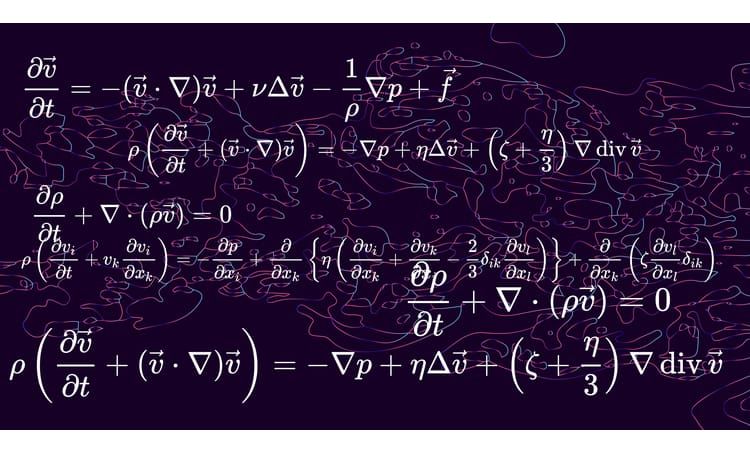

There is one area of mathematical physics and engineering that continues to challenge systems designers: fluid dynamics. Learn about the primary equations for compressible and incompressible flow in fluid dynamics in this article. bit.ly/339qI45 #cadence #CFD

English