The 3 wireshark MAC a0:b1:c2:d3:e4:f5 a8:b1:c2:d3:e4:f5 a9:b1:c2:d3:e4:f5

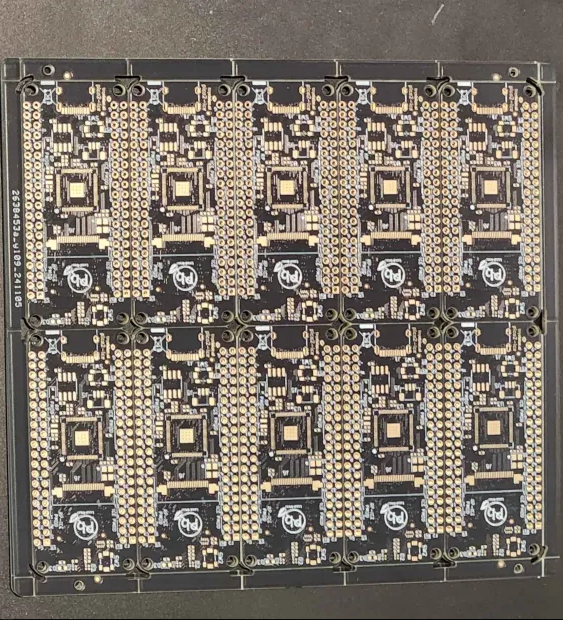

far bottom left pi3-28 with catboard iCE40HX8K

bottom center pico-ice bottom right pico-ice github.com/develone/pico-… github.com/develone/pico-…

English

Ed Vidal

212 posts