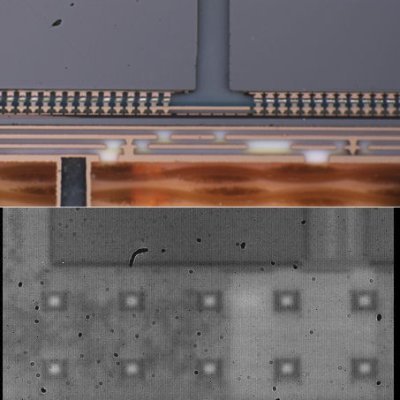

@highyieldYT Something like this,, and you’ll probably want to finish with a lot finer than 3 um

ultratecusa.com/product/ultrap…

English

Tom Wassick

1.4K posts

@wassickt

Semiconductor packaging engineering professional working on upcoming server technology while also watching chip and packaging technologies. Opinions are mine.

Rumor: The 4-die Rubin Ultra has been canceled, and only the 2-die Rubin Ultra will be mass-produced. It is still unclear whether this will result in a reduction in Rubin Ultra’s HBM capacity.

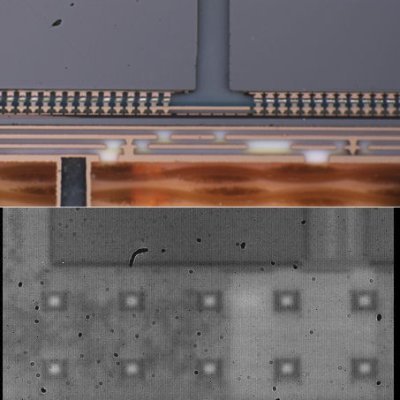

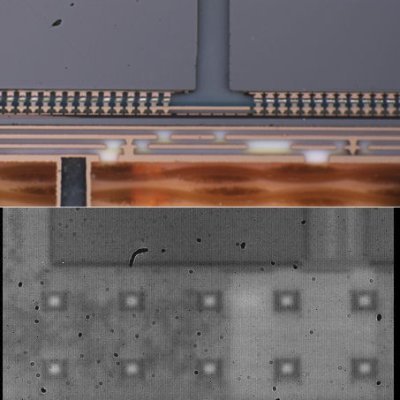

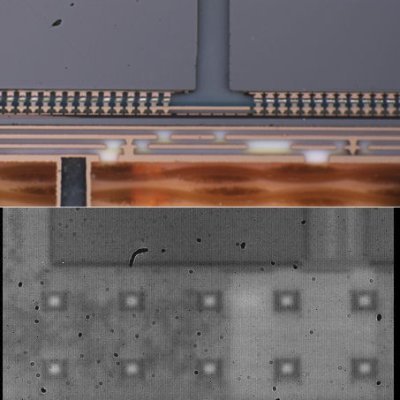

@rwang07 What the hell is Glass substrate DRAM?