witeken

19K posts

witeken

@witeken

Semiconductors and all things Intel. Legacy verified. Freelance @tomshardware @SeekingAlpha @VentureBeat (LFW). https://t.co/p0B1ljf2nP https://t.co/aRV0H7XRzl

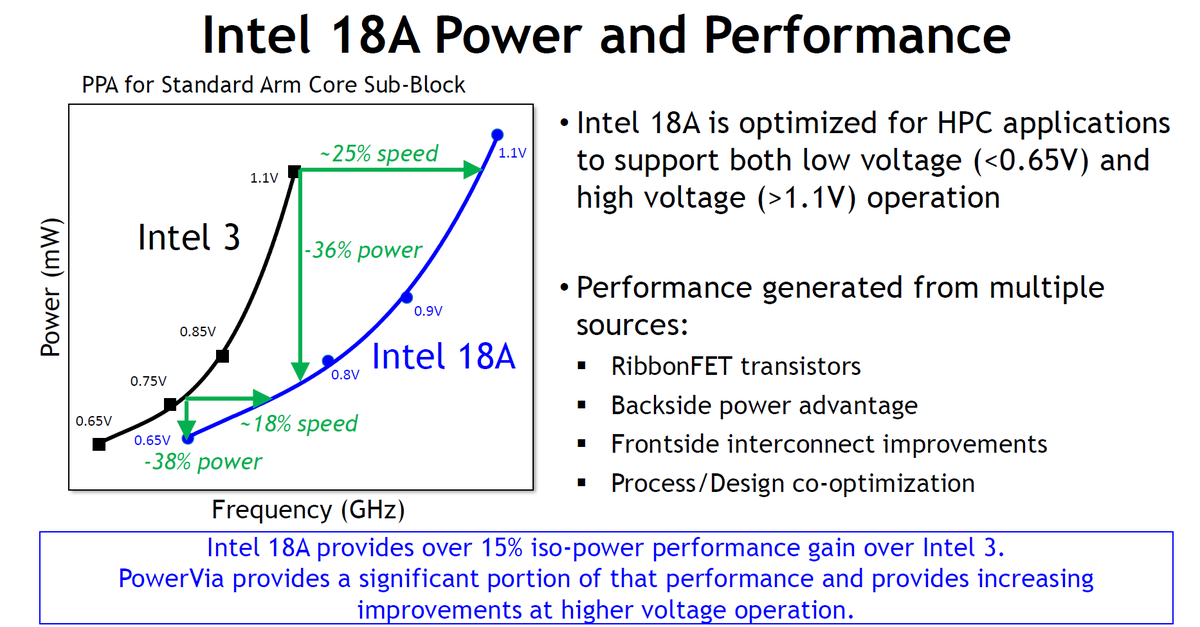

@witeken To be fair they are pulling in other things not density related. Intel went for performance on 18A and TSMC went for density on 2nm. Intel's 18A is more like TSMC's 3nm in logic density. It looks like both are going to focus on shoring up the short comings for 14A and A14.

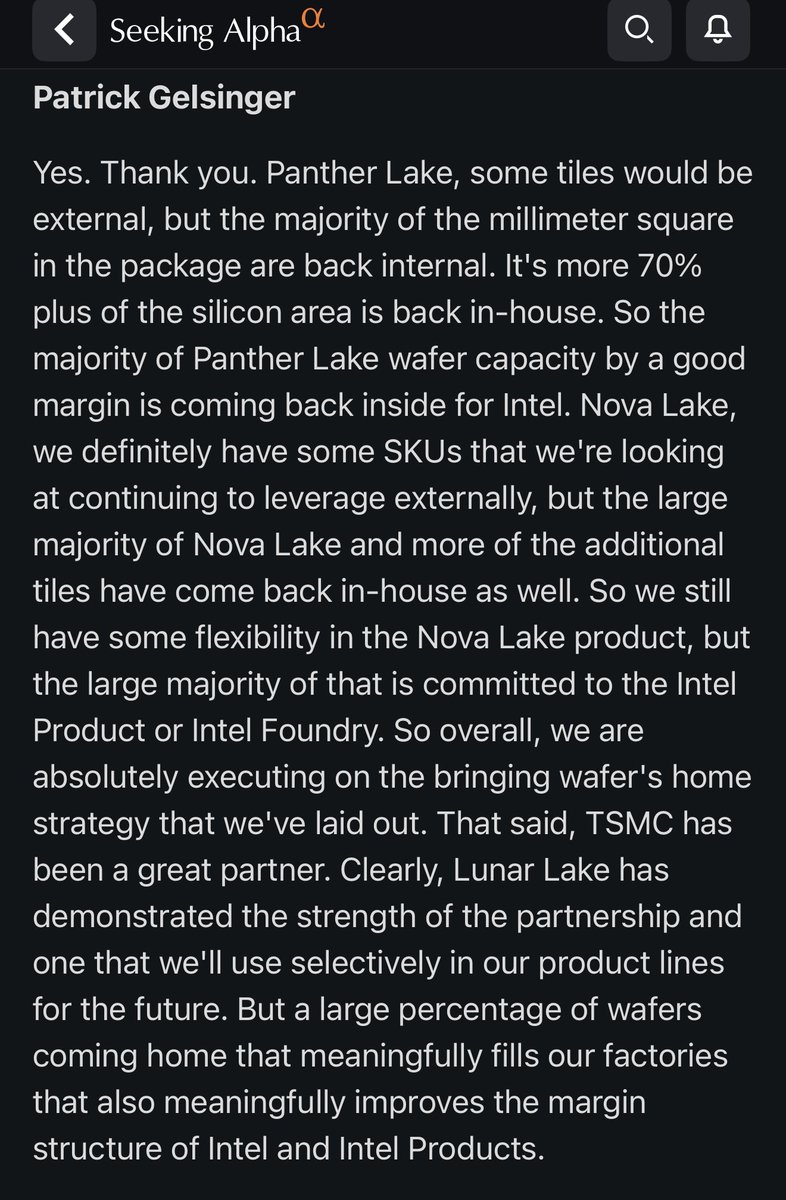

TSMC finally discloses A14. A few interesting notes. One, highligting the value to smartphones. Two, bearing in mind one customer (monolithic designs) will absorb 70+% of these leading edge capacity/wafers for two years.. Intel will have leading edge available, for HPC and chiplets/dissaggregated design. pr.tsmc.com/english/news/3…

Today, Mobileye released its financial results for the three months ended in March 29, 2025. Read more here: bit.ly/4jlURyB

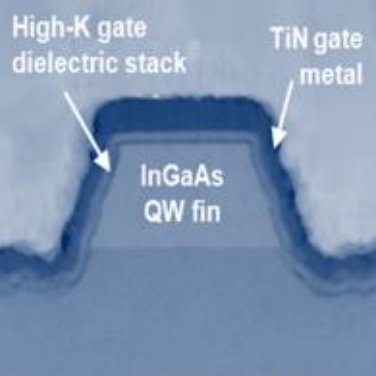

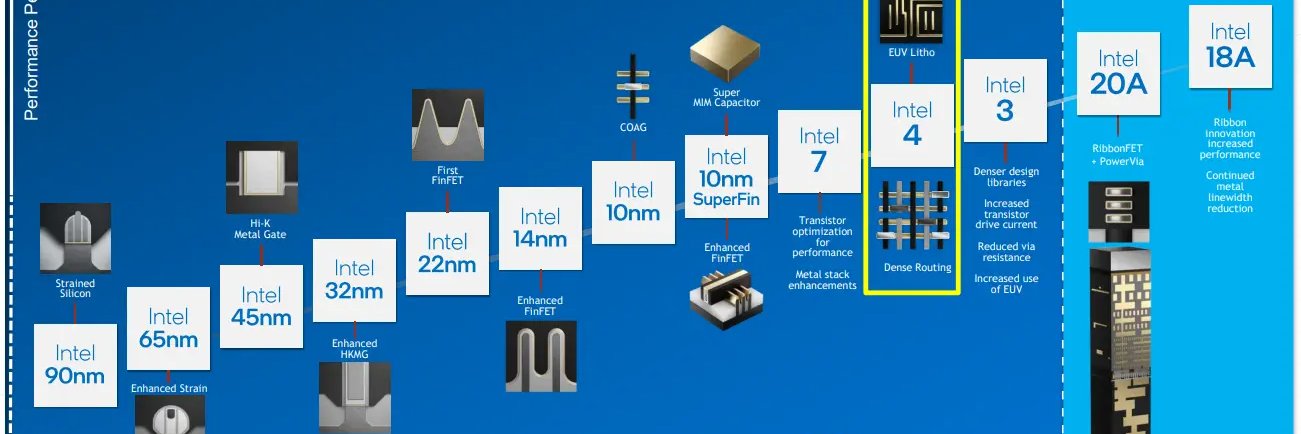

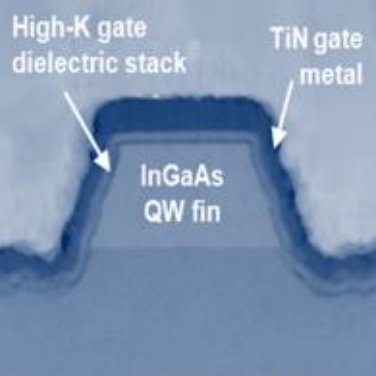

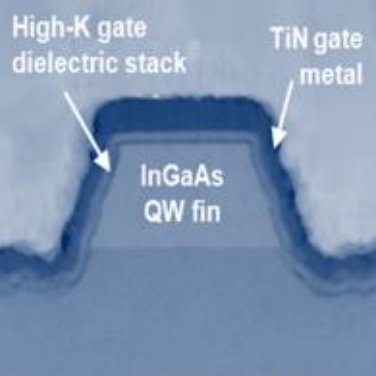

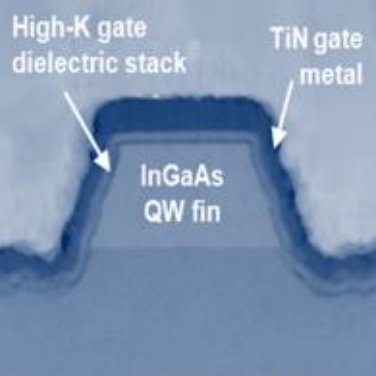

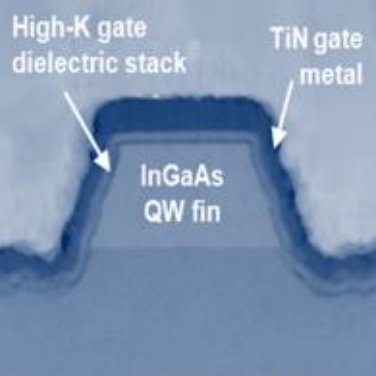

Some Technical Highlights 2025 VLSI Intel 18A RibbonFET(GAA) and PowerVia(BSPDN) - over 30% density scaling and a full node of performance improvement compared to Intel 3 IMEC Advanced Packaging - frontside hybrid bonding 250nm pitch and backside through-dielectric vias to 120nm pitch TSMC PMOS with Monolayer WSe2 Channel Samsung Tungsten-doped Indium Oxide MOSFET with 3 Angstrom EOT Samsung 9th Gen 1Tb 3D NAND - 286-Layer. Bit density improved by 50% than previous gen. Micron Ferroelectric NVDRAM - x- and y-direction ptich 41nm. ferroelectric stack 5nm - array operation voltage R/W at 1.4V TSMC 0.75V Vdd Oxide-Semiconductor 1T1C KAIST 4.8~9.6 mJ/frame NuVPU - Nerual Video Codec with 36.9 TOPS/W NVIDIA 77 fJ/bit 8Gbps D2D Link in 3nm - Energy efficiency of 77fJ/b, 44Tbps/mm2 at 0.7V in 3nm process University of Michiga 256-point FFT engine 0.71nJ, 1.53GS/s TSMC 3nm FinFET 35.5Mbit/mm2 - HD 6T SRAM for mobile - 3nm FinFET test chip 17% reduction in active energy 10% decrease in standby leakage Intel 128Gb/s 0.67pJ/b PAM-4 in 18A - 18A CMOS process integrated 128Gb/s DAC-based TX - 0.67pJ/b bit efficiency, 0.75pJ/bit with the PLL Full PDF is here: vlsisymposium.org/wp-content/upl…