پن کیا گیا ٹویٹ

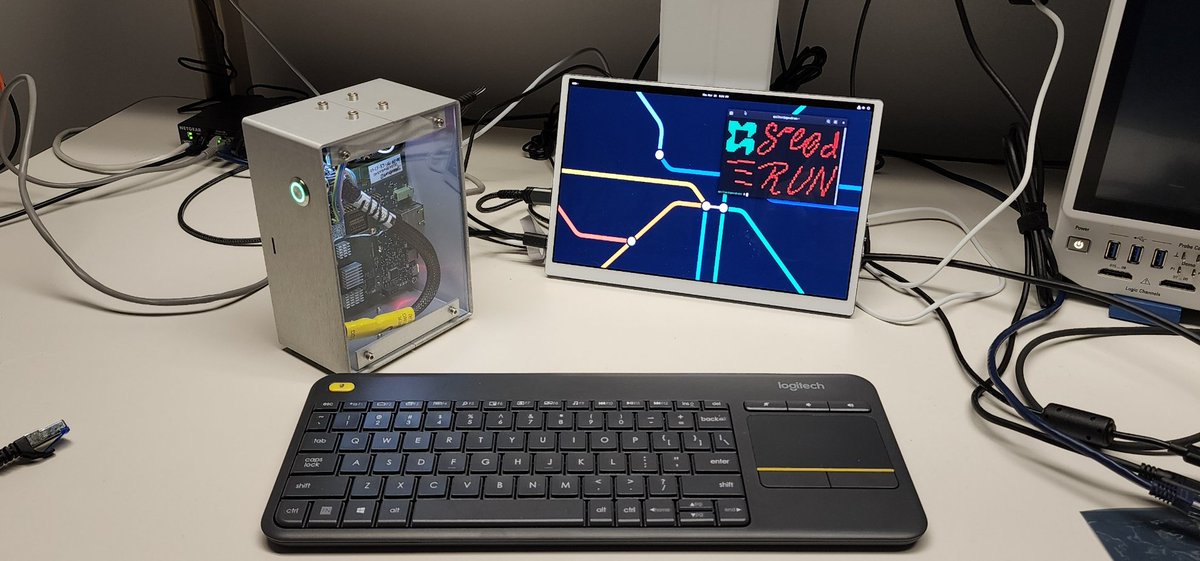

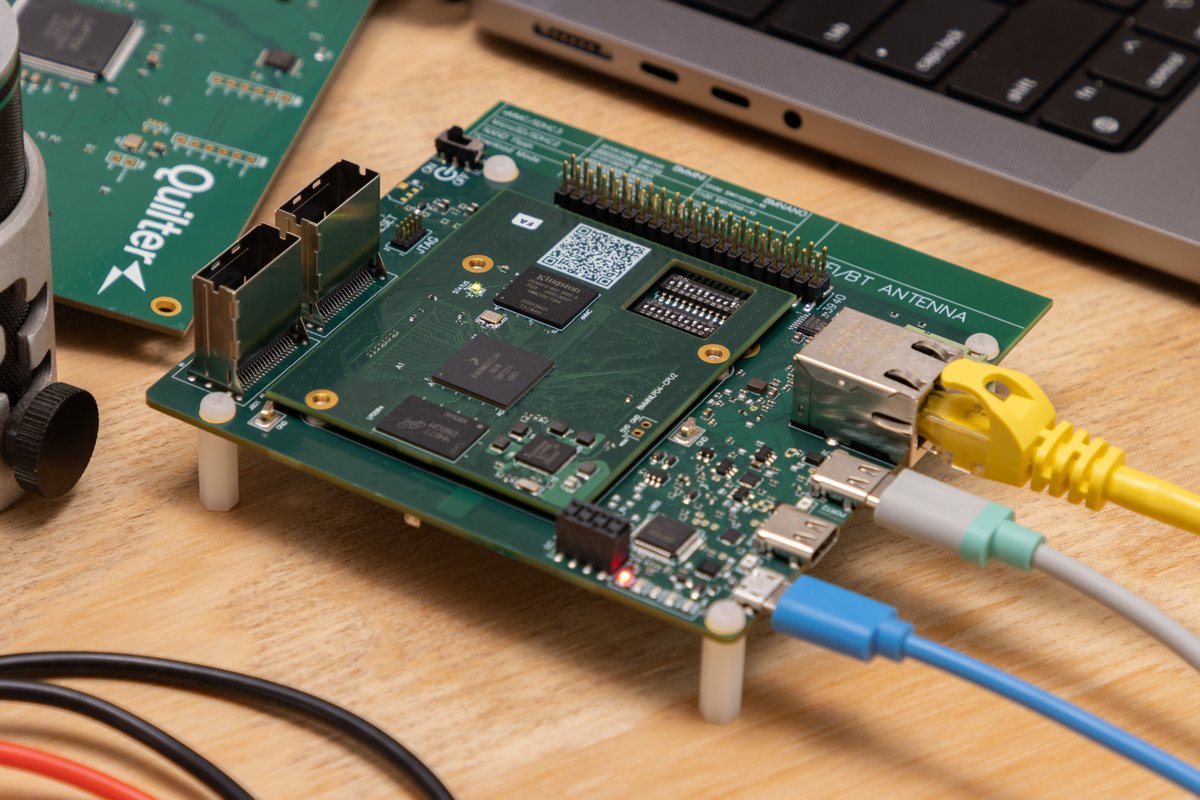

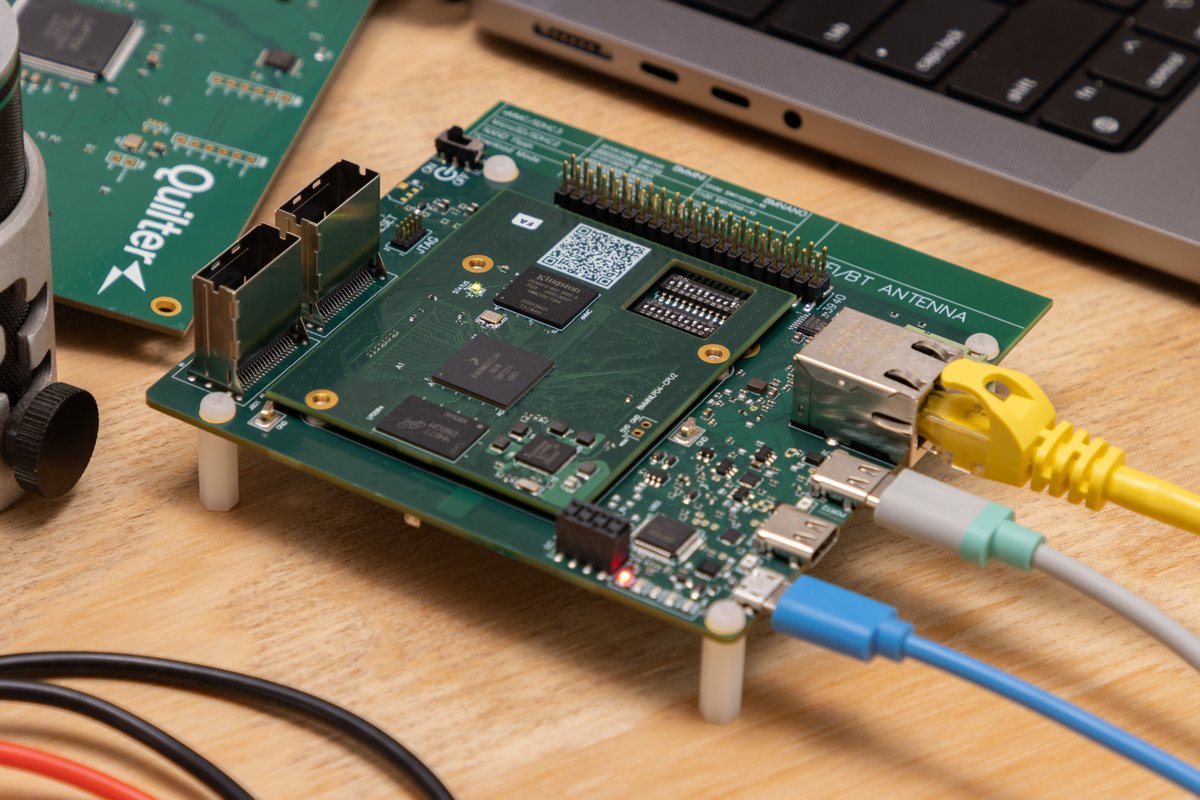

@quilterai just hit a milestone we've been working toward for years:

An AI-designed, 843-component Linux computer… that booted on the first try.

This is Project Speedrun — the hardest test we’ve ever thrown at Quilter.

👇

English

Sergiy Nesterenko

155 posts

@sergiynest

Using reinforcement learning to build hardware @ quilter ai

AI:AM Takeoff x.com/i/broadcasts/1…

Quilter's physics-driven AI is getting better fast. Register for a live walkthrough on April 23rd. Here's everything we shipped in Q1 2026: - Calculated impedance profiles (Simbeor) - Ground net comprehension and region ground pours - Restructured setup flow with computed constraints - Single stackup per job - New full-screen candidate reviewer Coming next: clearance constraints from uploaded files and automated BGA fanouts. quilter.ai/changelog