固定されたツイート

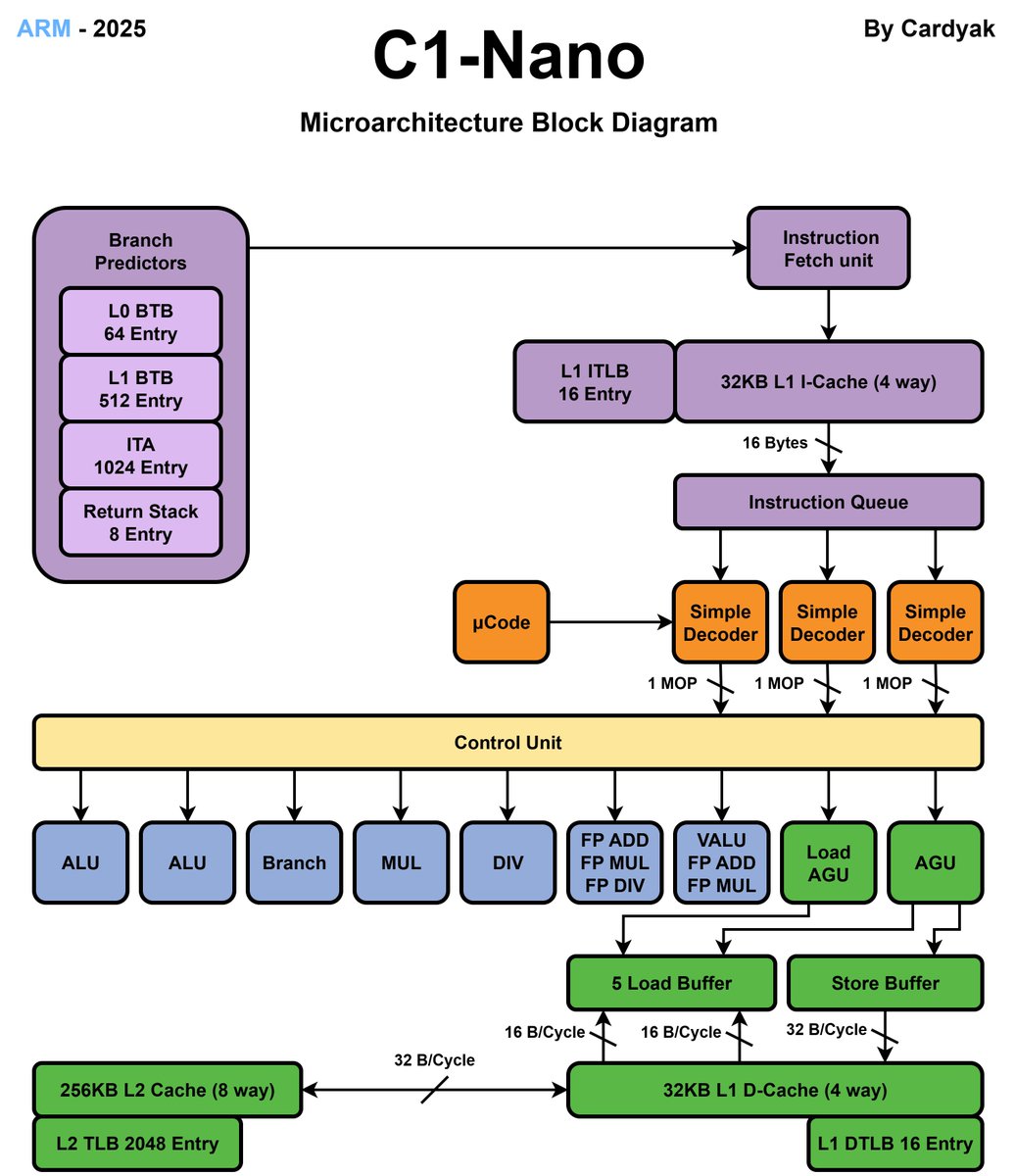

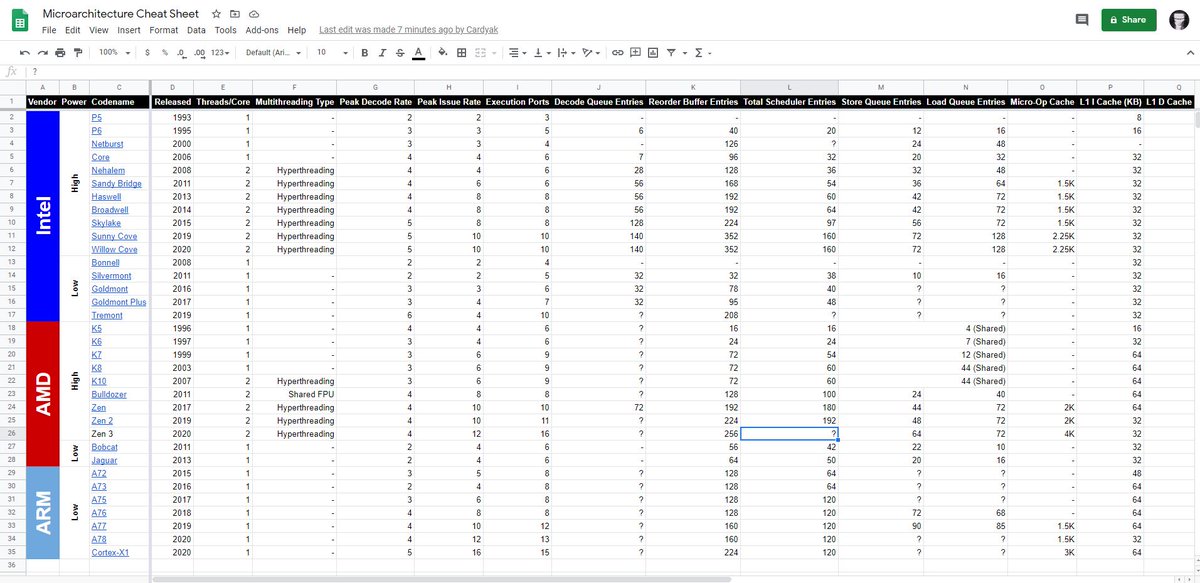

Inspired by @InstLatX64, today I'm introducing the #SiliconGang Microarchitecture Cheat Sheet: bit.ly/2JTplfJ

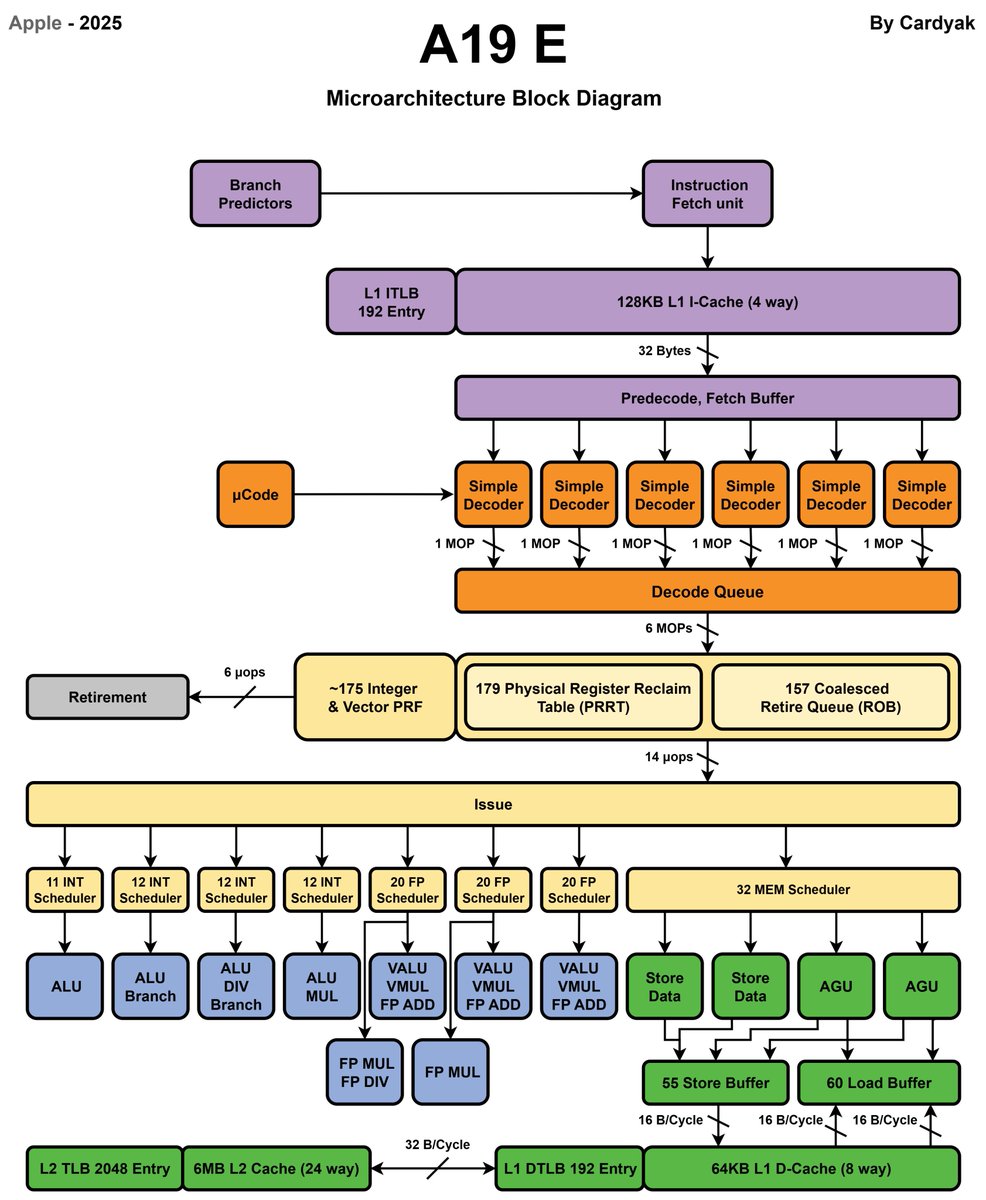

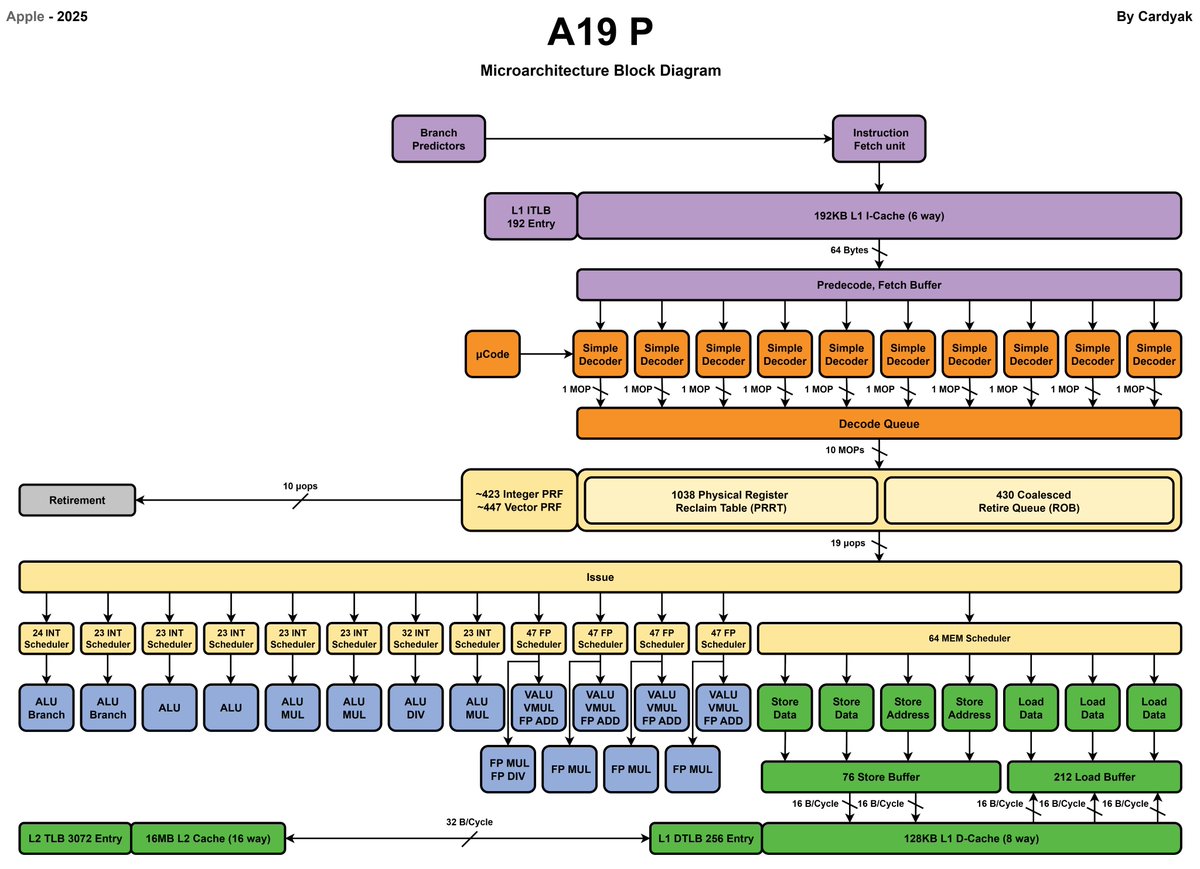

This can be viewed by all, and it offers centralised information about CPU μarch design such as caches, buffers, instruction width, etc.

Some notes below:

English