ON_AI_Foundry

116 posts

@ON_AI_Foundry

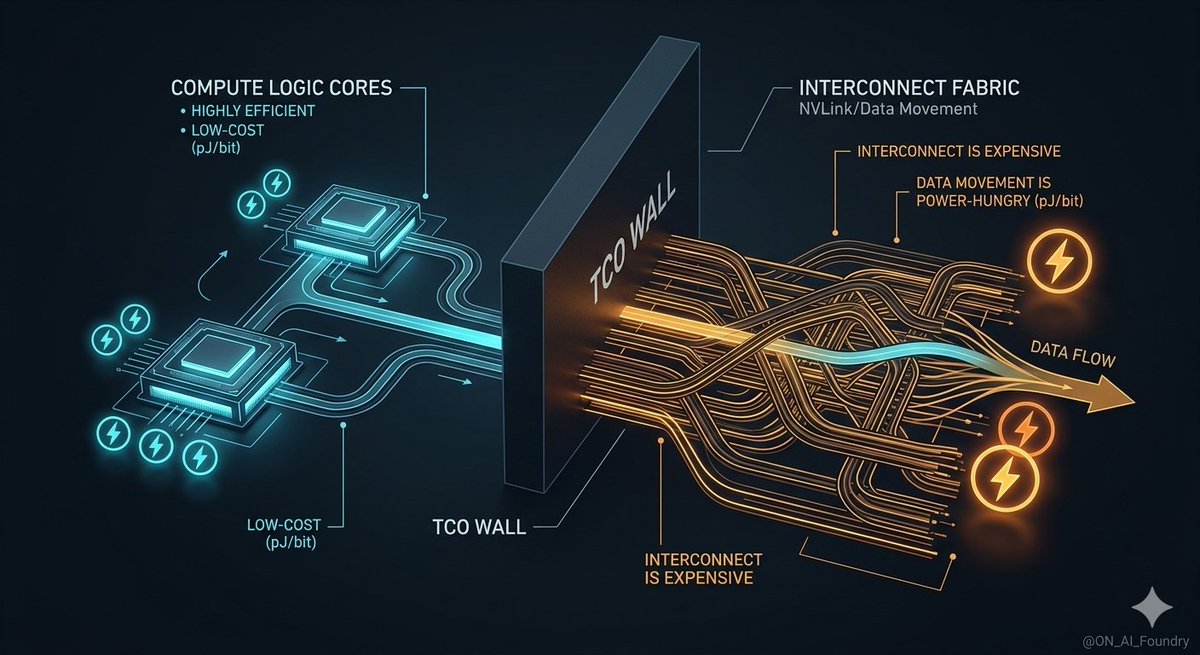

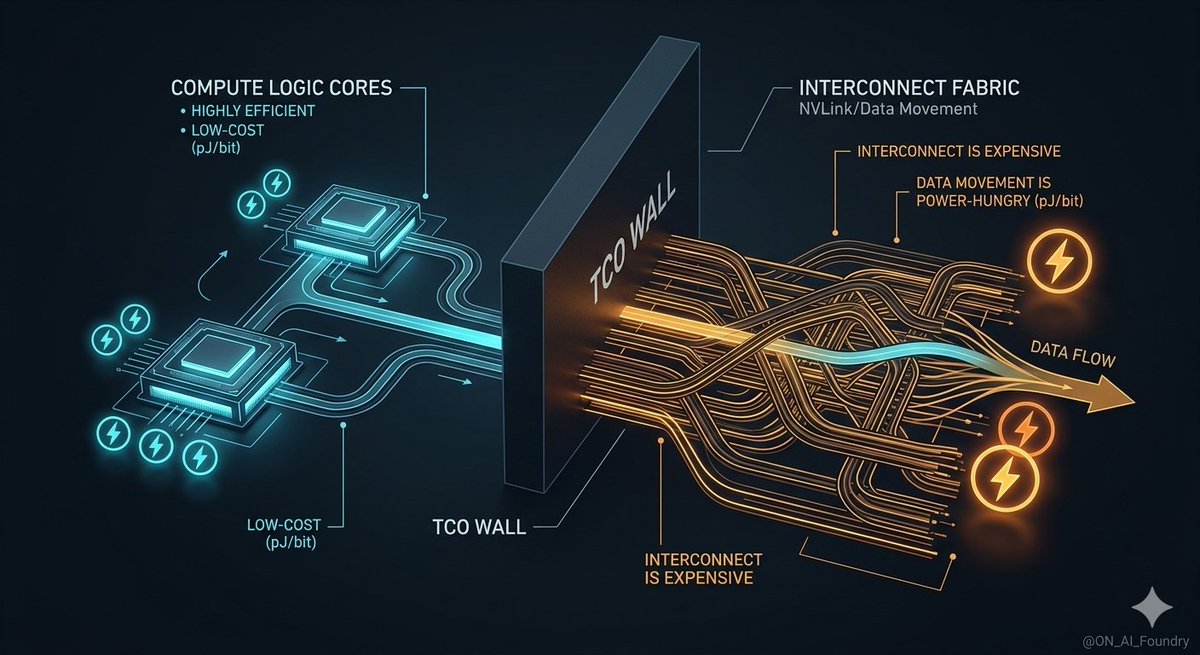

Decoding AI Infra @ Silicon level. pJ/bit • Memory Walls • 1.6T Fabric. Turning noise into Alpha for the 1%. Follow for the data others miss.

Something that people making AI economics predictions should take into account is that 1) current AI use is heavily subsidized, 2) demand for smart, compute-heavy models is exploding w/ few price signals to discipline use, 3) we will be hitting serious compute constraints soon. Translation: We have been living through a period of abundant AI; get ready for the age of compute scarcity. There will be more rationing, multi-tiered markets, new token allocation infrastructure, etc.

The US needs 500,000 new electricians this decade. Apprenticeships take 5 years. Microsoft’s Brad Smith says it’s the #1 thing slowing data center expansion. The AI bottleneck isn’t chips. It’s the trades.

@nummanali tmux grids are awesome, but i feel a need to have a proper "agent command center" IDE for teams of them, which I could maximize per monitor. E.g. I want to see/hide toggle them, see if any are idle, pop open related tools (e.g. terminal), stats (usage), etc.