Sabitlenmiş Tweet

Moving my old Android app project from java to android jetpack Compose (Kotlin)

#JetpackCompose

English

techyed

930 posts

@Techyed_

advance technology, deep tech innovations, powering startups, building AI inference chips

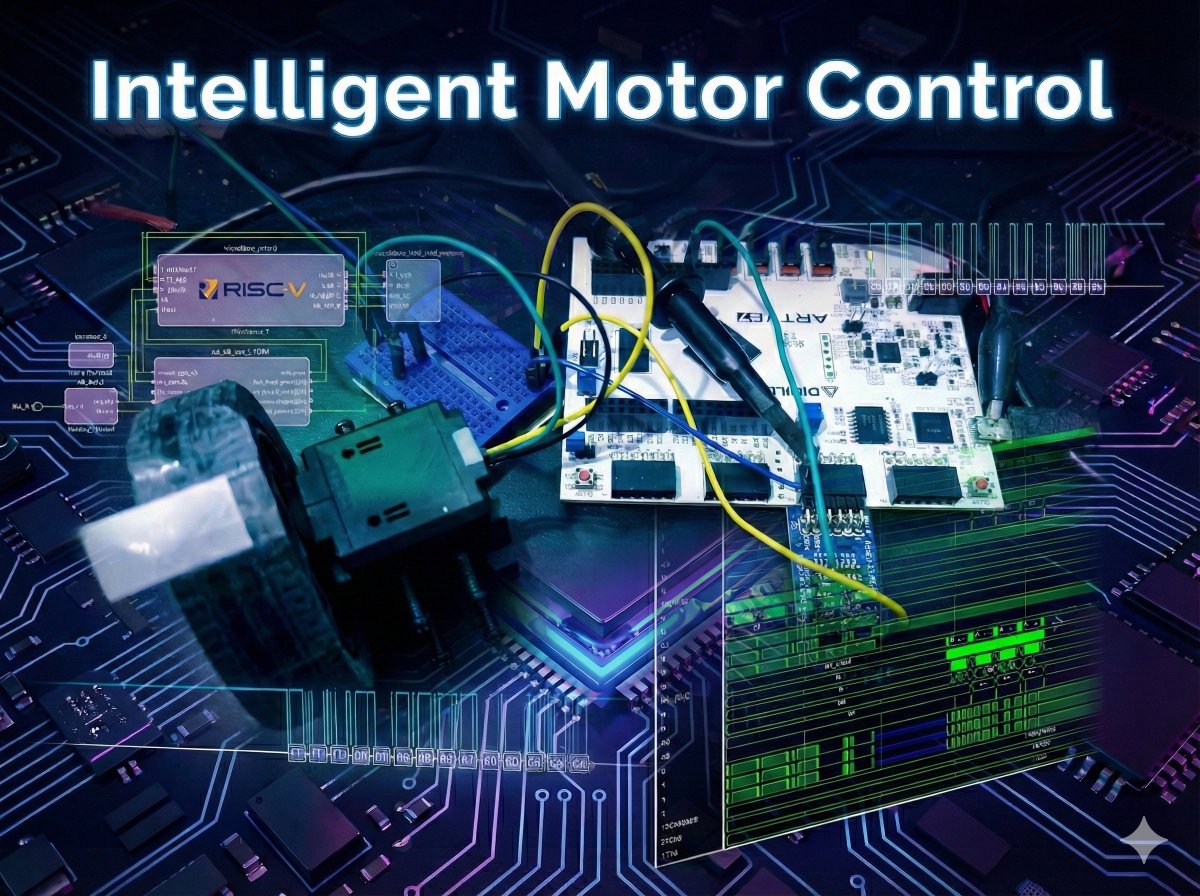

Solved in system verilog