Sabitlenmiş Tweet

Swaroop Kumar Yadav

1.8K posts

Swaroop Kumar Yadav

@S2SmeX

Ex-Intern @TRAI | Documenting projects & learning | Building in public 🚀 Open to VLSI/Embedded roles @swaroop2sky

Katılım Ekim 2022

143 Takip Edilen295 Takipçiler

@ATaylorFPGA If i want to use an ov7670 camera, what changes do I have to make?

Just curious...

English

@GusEmmett Lattice impressive.

I'll buy things like this someday 🥲

English

@S2SmeX Okay. So you dont have to do that in HLS.

Complete you block diag. Crate hdl wrapper -> generate output products -> generate bit stream -> export hardware with Bitstream.

Than create a project in vitis ide with with this xsa. And pickup hello world boiler plate. And program.

English

I have updated it a bit, but can't understand so many things. can anyone suggest me a good tutorial on it.

Swaroop Kumar Yadav@S2SmeX

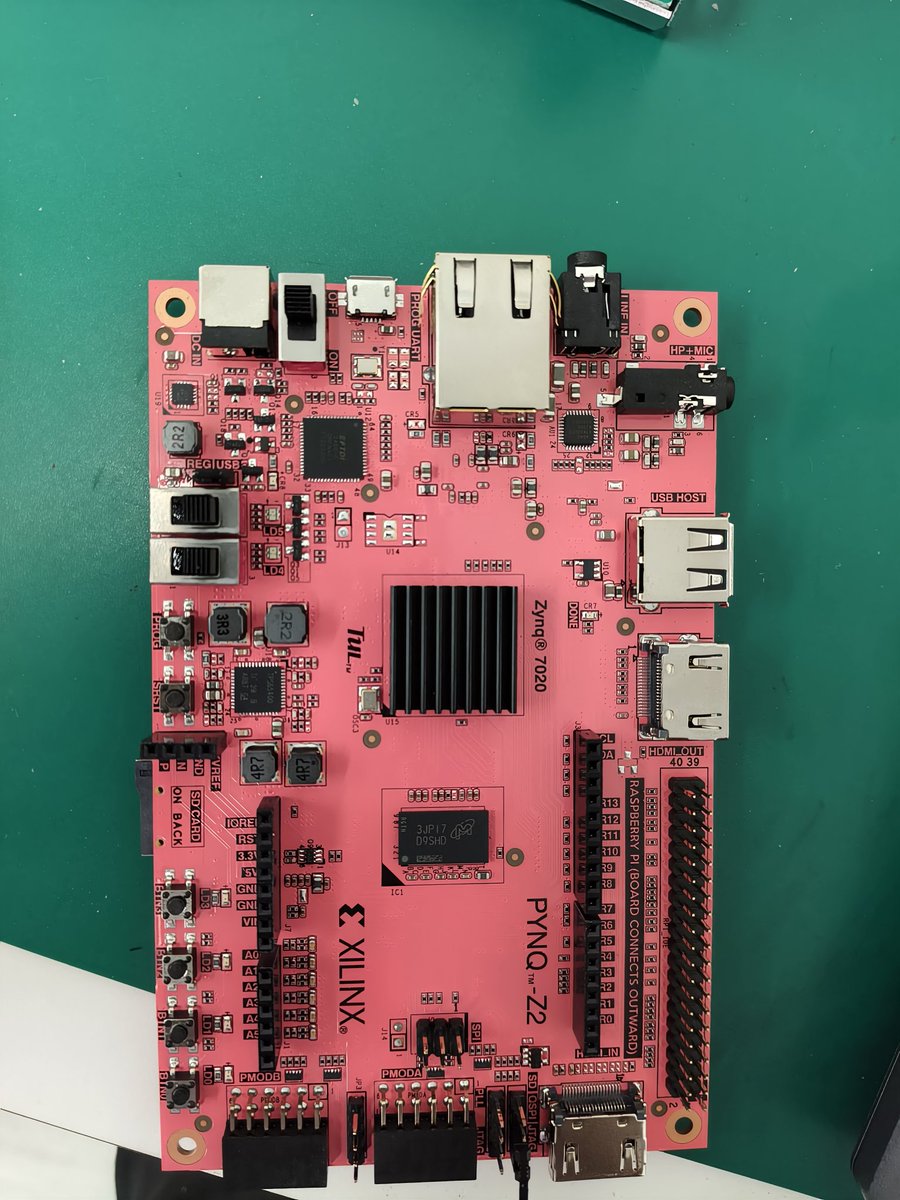

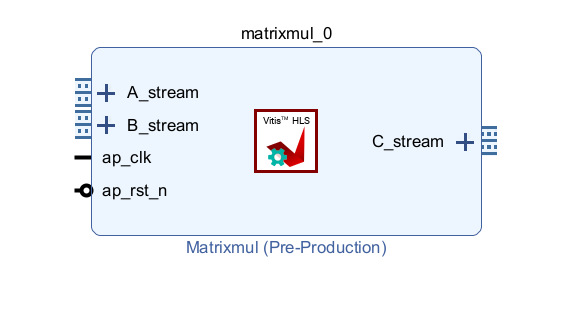

made my first IP : A N-number Matrix multiplier

English

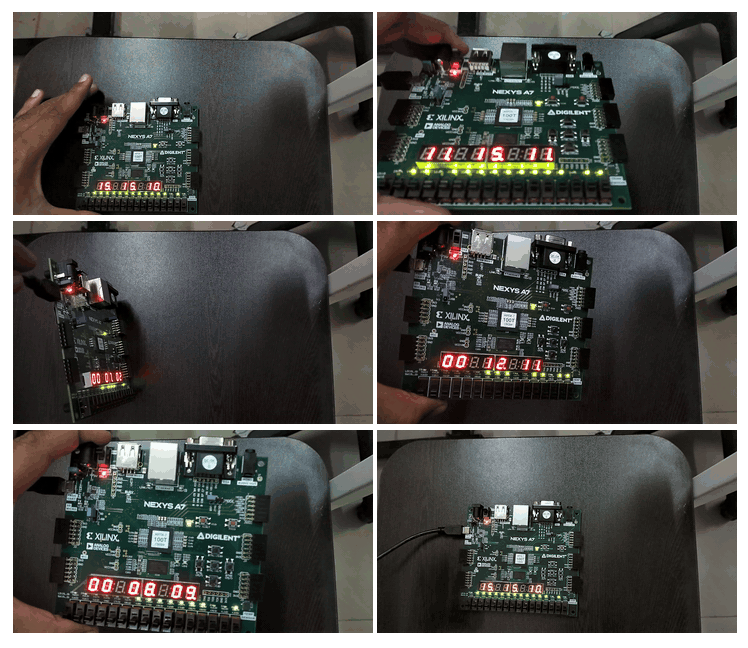

Sharing glimpses of my previous project: I interfaced on board Accelerometer (Nexys A7 FPGA) and display x,y,z data on 7-segment display.

check out more on : SwaroopKumarYadav.in

English

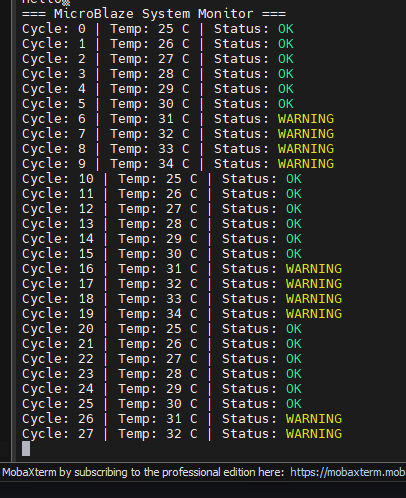

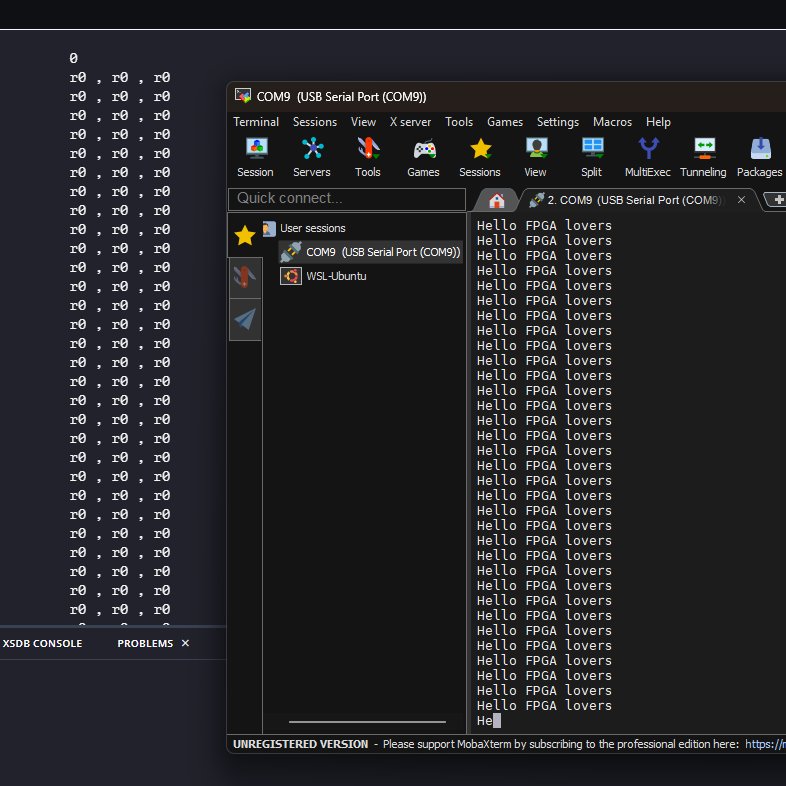

Finally it's working. My very first program running on a FPGA with VITIS HLS.

It was stressful at first, but @X community is awesome.

Thank You so much guys.

English

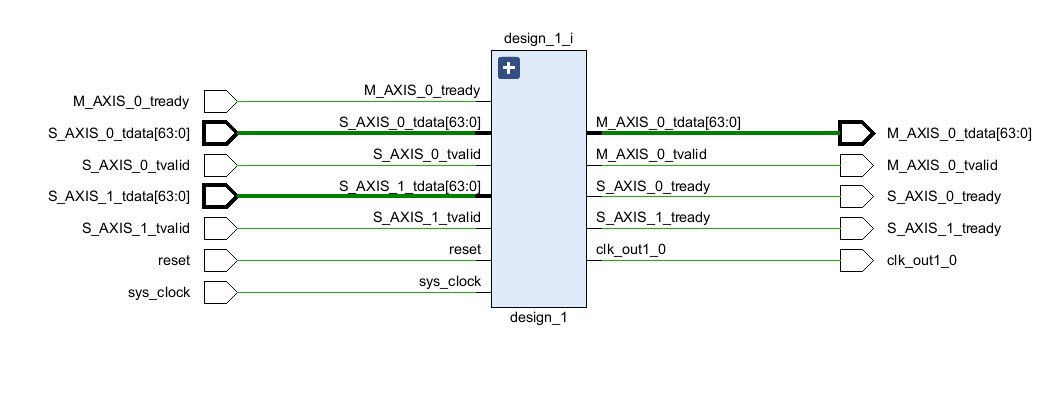

@_prashantbagri I thought I would export it after making it into a proper package. Am I in the correct direction?

English

@_prashantbagri Not in this project. I tried it once, that one is another mess. But somehow I did it.

So should I export this ip back to Vitis but shouldn't I add other elements like clock, reset, fifo...

English

@_prashantbagri Ok can we do that.

Cause I was making use of that IP in a block diagram with axi FIFO to trigger inputs to my IP and generating hdl out of it.

Can you share any resources, any tutorial or any structured videos.

English

@Benathon Yes I made it to some extent, dealing with some clock and reset issues.

But don't you think hls is far more scalable.

You just have to update your cpp code.

English

@_prashantbagri Actually I got frustrated, I made this simple matrix multiplier in Vitis and packaged it as IP. Now trying to use it via vivado in order to test on FPGA.

I really need a tutorial or guidance, cause currently it's just me & chatgpt.

English

@_Wolf25_ Wokwi, tinkercad are awesome. I just found this new website and loved it.

English

A very well made online IDE for embedded prototyping.

velxio.dev

English

@rohith1994kc I think of each block as an individual IC, like I am packaging my design into an ic and these are its pins, the best thing, I can design those pins as per my requirement. This analogy makes things easier for me.

English

@S2SmeX How to understand that block required for embedded people to work ??

English