Shamim

1.5K posts

Shamim

@ShamimKeshani

🎓 Started in electronics → fell in ❤️ with programming → became a FullStack Engineer → changed my life/work → now sharing the journey publicly

LinkedIn → Katılım Mart 2018

199 Takip Edilen134 Takipçiler

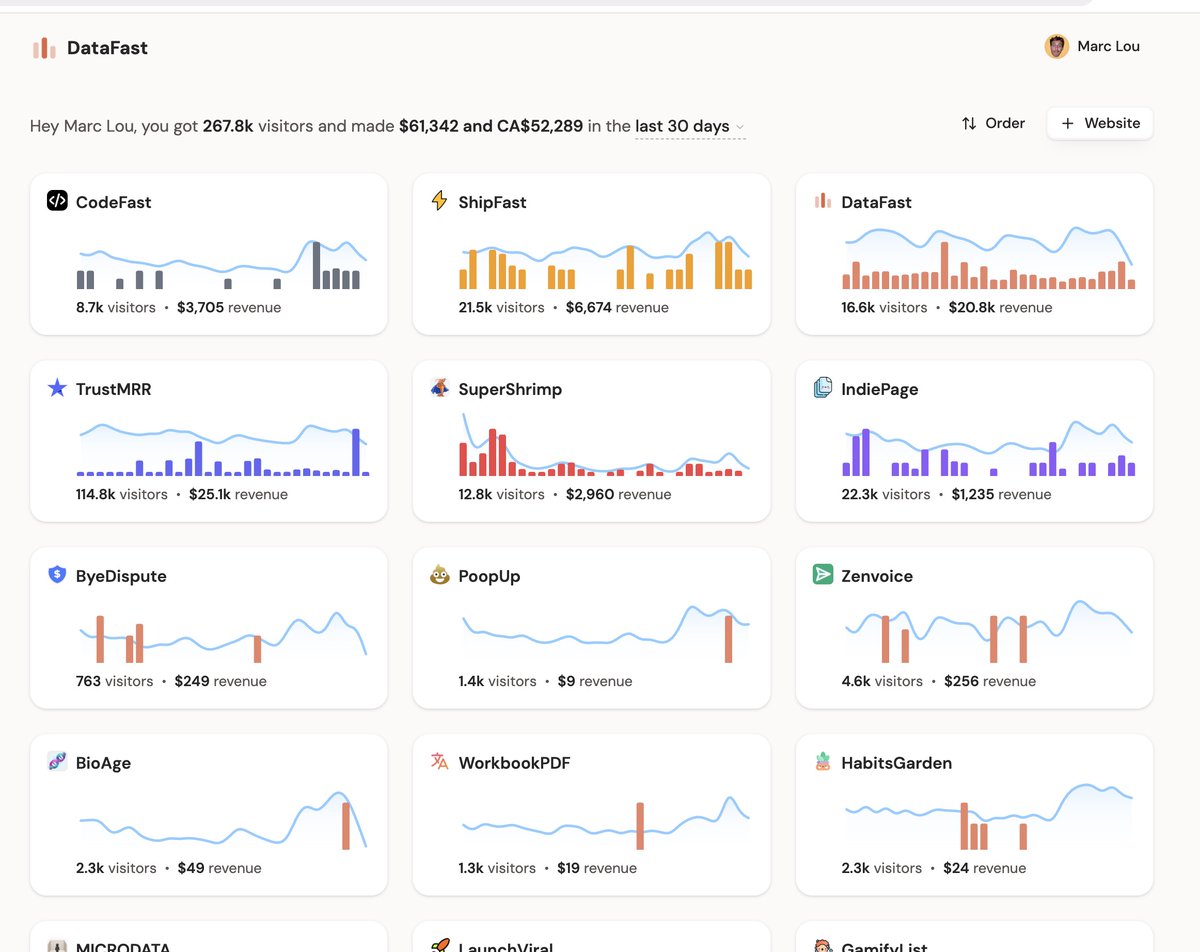

AI suggests building my own api thing. Should we ask @marclou to help us?

We love you, @marclou, build this for non-premium users! Pretty please. 😊

Shamim@ShamimKeshani

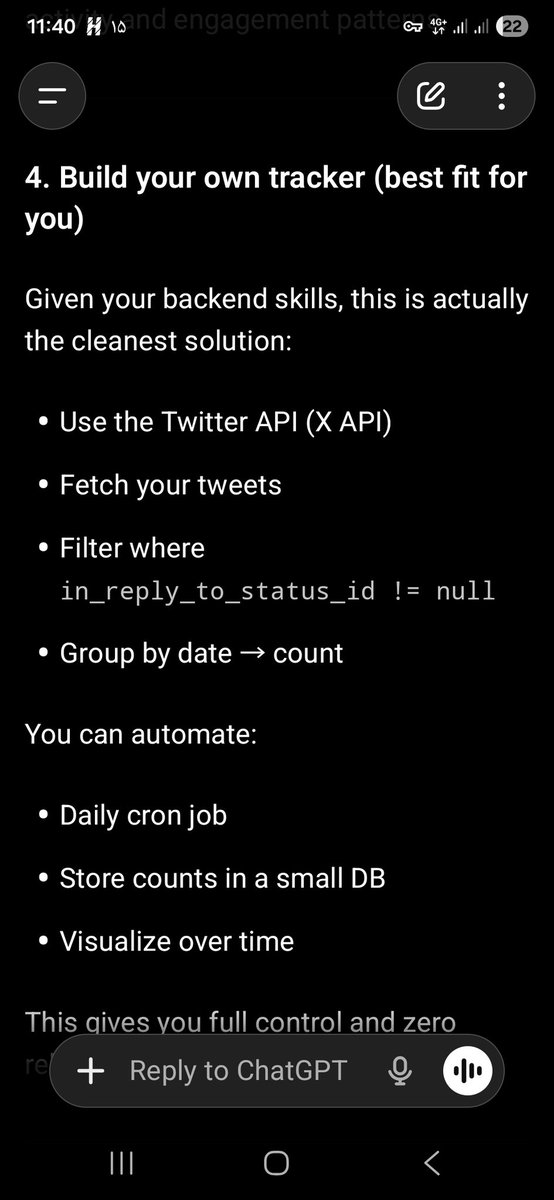

How can I get my reply count per day if I'm not premium?

English

@theyfwstoner @Neovim Not much. I'm more of an email guy! Important -> email

English

How can I get my reply count per day if I'm not premium?

Razvan Andrei Cureteu@cureteurazvan

I started taking X seriously on March 17. Since then, I’ve gained 300+ followers. Not life changing. Not viral. Just proof that showing up consistently works. Better than yesterday. That’s the game.

English

@sickdotdev Next question: while we are at it, let's recommend some good movies too!

English

I'll have a question for you. I see you also followed the reply strategy and got results (like many others said to do so). What were the replies you provided? Short Support? Your opinion? General advice? On average, how lengthy were they? Thanks.

(Your answer could be a nice guide that you can share: from 0 -> 300)

English

I'm just pasting these here from my resume:

Ph.D. in Electrical Engineering

July 2015 — June 2021

Summary of Thesis:

This thesis aims to develop a frequency extractor processor for DIFM receivers to improve frequency accuracy and pulse detection speed. Initially, the MMSE estimator was used, enhancing frequency extraction but being computationally intensive. The new InReDI methodology was introduced, achieving high reliability and speed. An industrial 15-bit DIFM receiver tested with InReDI demonstrated an 8.3 million pulse detection speed and 11 MHz frequency error. Combining MMSE with Piecewise Linear Approximation and InReDI resulted in a final architecture with a 1.43 MHz accuracy, implemented on a Xilinx Artix7 FPGA, achieving 2.7 million pulses per second.

Master of Science

September 2010 — August 2013

Summary of Thesis:

This research focuses on developing an artificial neuron, the basic computational block of artificial neural networks, using nano-scale technologies. Targeting mobile applications and low energy consumption, the design is implemented in the sub-threshold region of CMOS technologies to significantly reduce power usage, though this may affect reliability. The study includes constructing reliable, low-energy logic cells, building neurons from these cells, and optimizing neuron parameters for specific applications like handwrittendigit recognition. A comprehensive software platform supports building, training, and testing these neurons. After optimizing the neuron design, it is synthesized using a specialized sub-threshold library, with performance and power consumption results reported, bridging detailed circuit design and high-level neural network application.

English

Deep down, you should know you did everything you could to make it work.

But that’s not how life works.

You stop.

You blame yourself.

You blame the universe.

Then you let it go.

You figure out what worked and what didn’t.

You change course.

You start again, in a new direction, with wisdom you didn’t have before.

English