NEW PHOTOS: The man who opened fire at an Austin, Texas bar overnight. 2 dead, 14 injured. Ndiaga Diagne, a U.S. citizen born in Senegal, wore a shirt saying "Property of Allah". His undershirt referenced Iran.

kariy ⛩️

2K posts

@ammarif_

doing stuff @ohayo_dojo @cartridge_gg

NEW PHOTOS: The man who opened fire at an Austin, Texas bar overnight. 2 dead, 14 injured. Ndiaga Diagne, a U.S. citizen born in Senegal, wore a shirt saying "Property of Allah". His undershirt referenced Iran.

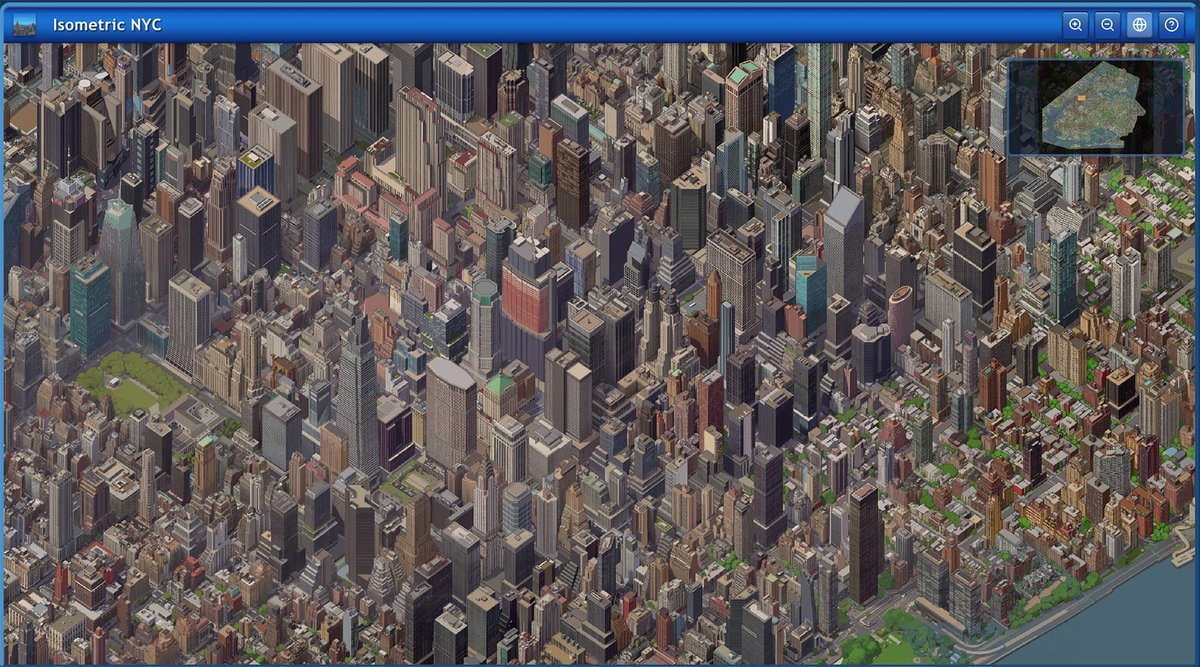

Largest NYC subway campaign ever Happening now

The question: "Why do CPUs have multiple cache levels?" often gets many CS students and professionals thinking and researching. This article from Fabian Giesen narrates a "cache story" in a relatable way, only to delve into the details - a must-read! fgiesen.wordpress.com/2016/08/07/why…