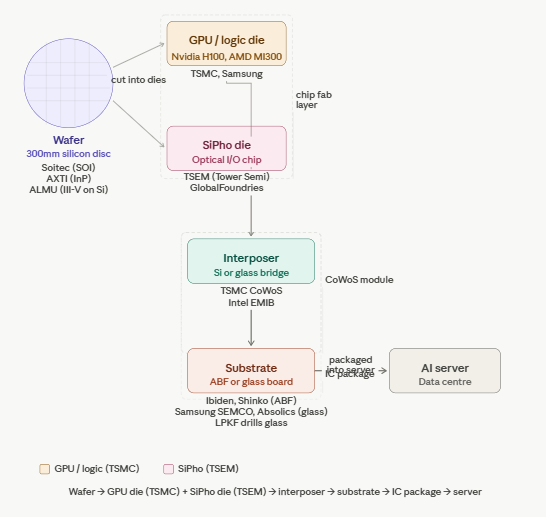

Photonics is a bit confusing, hopefully this simplified summary helps. I have positions in $TSEM, $SOI, $ALMU, $LPKF

Ayman

217 posts

Photonics is a bit confusing, hopefully this simplified summary helps. I have positions in $TSEM, $SOI, $ALMU, $LPKF

TSMC announced the latest A14 (1.4nm-class, backside power delivery) process data at the European OIP Forum. Compared to N2 (2nm-class), it delivers a 16% performance boost at the same power and a 27% power reduction at the same frequency, surpassing prior estimates of 10-15% performance gains and 25-30% power savings. The slides list only mainstream nodes, omitting updates for intermediate nodes like N3B (used mainly by Apple and Intel), N3P, and N2P. While dedicated nodes such as N3X, N2X, and A16 are mentioned, skipping intermediate updates downplays their incremental value. Compared to N7 in 2018, A14 delivers 1.83x performance and 4.2x power efficiency over roughly a decade, confirming Moore's Law is slowing but still alive. TSMC notes each major node cuts power ~30% with steady 15-18% performance gains; recent focus has clearly shifted to power efficiency. AI-driven EDA tools are becoming critical. Using reinforcement-learning APR tools like Cadence Cerebrus and Synopsys DSO.ai for placement, routing, and metal stacking alone yields ~7% additional power savings—equivalent to one full intermediate node upgrade.

Photonics is a bit confusing, hopefully this simplified summary helps. I have positions in $TSEM, $SOI, $ALMU, $LPKF

Photonics is a bit confusing, hopefully this simplified summary helps. I have positions in $TSEM, $SOI, $ALMU, $LPKF

Furukawa Electric trading at 20x PE always surprises me

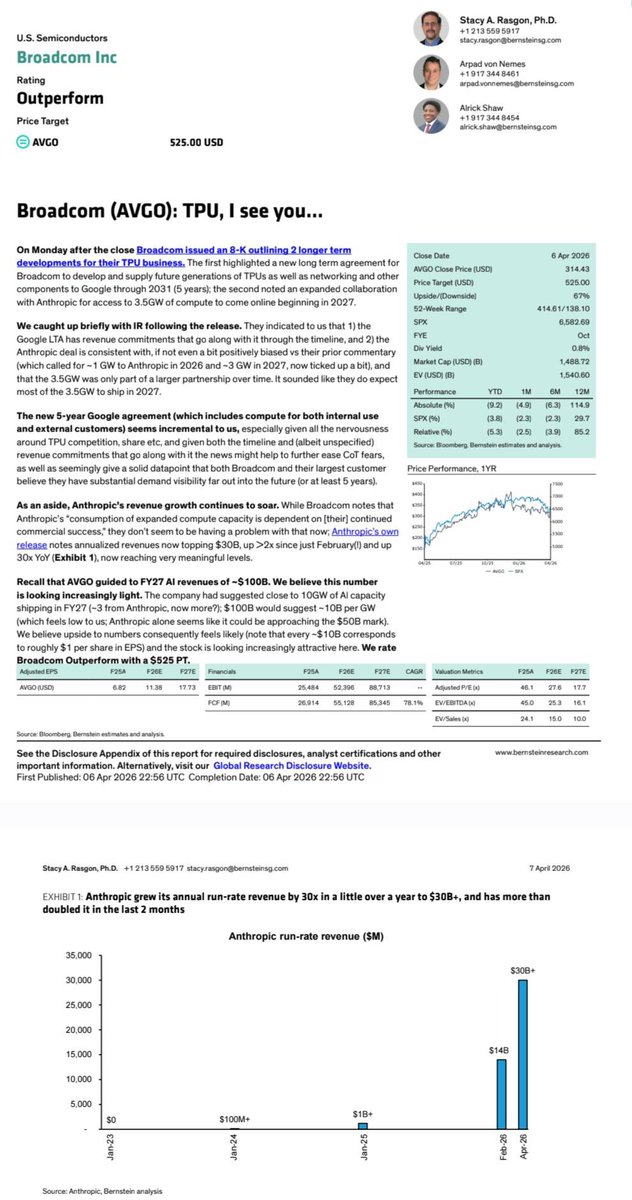

KeyB from -ve $AVGO to +ve: "This represents a material increase from the prior October 2025 announcement, which contemplated "well over one GW" of compute in 2026, and is modestly above mgmt's prior earnings-call commentary that Anthropic could exceed 3 GW in 2027"