Jeff Smith

1.4K posts

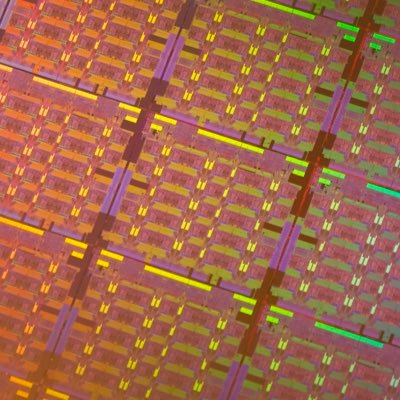

M4 Ultra designed for the Mac Pro has been hinted to feature up to an 80-Core GPU, as Apple said to be in a better position to enter the mainstream gaming market wccftech.com/m4-ultra-for-t…

NEW BLOG! "The PS5 Pro, RDNA 4 & FSR 4.0". This one is two things at the same time: a well-edited overview of lots of recent news & explainers, and my speculative instincts gone wild. No, you can't have the useful and correct part without the crazy part. link.medium.com/beuSHErldOb

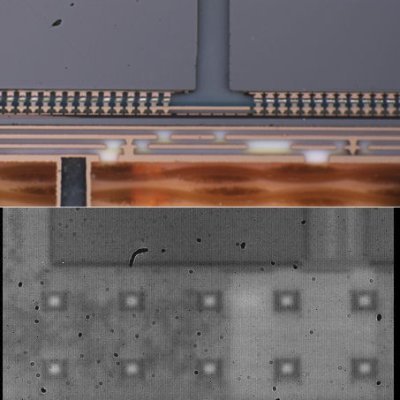

In his announcement @jackhuynh is confirming the SRAM chip is now sitting below the CCD for the Ryzen 7 9800X3D. By the looks the SRAM chip also has the same size than the CCD. But it then also does need to interface signals and power for the CCD, right?