Cologne Chip AG

22 posts

@matt_rambling We are working on the integration for nextpnr.

English

@colognechip Very exciting. But why do you use a proprietary place and route tool? Seems like open sourcing that, or working with existing open source P&R would be both easier and better for you and your users.

English

There is a new video from the community showing the first steps with our GateMate Evaluation Board.

youtu.be/LWvO5AiTUng

YouTube

English

@DurandA23 @Olimex Hi, yes nextpnr implementation is still in pipe. We cannot give a date yet. But it will come soon.

English

@colognechip @Olimex Thank you for providing a sane lightweight toolchain. Is a nexpnr implementation still in the pipe?

English

“People who are really serious about software should make their own hardware.“

Cologne Chip is featured on the page 34. Very interesting overview!

#fpga #colognechip #armasuisse #electronics #foresight #innovation #imagination

bit.ly/3KKU6A8

English

Cologne Chip AG retweetledi

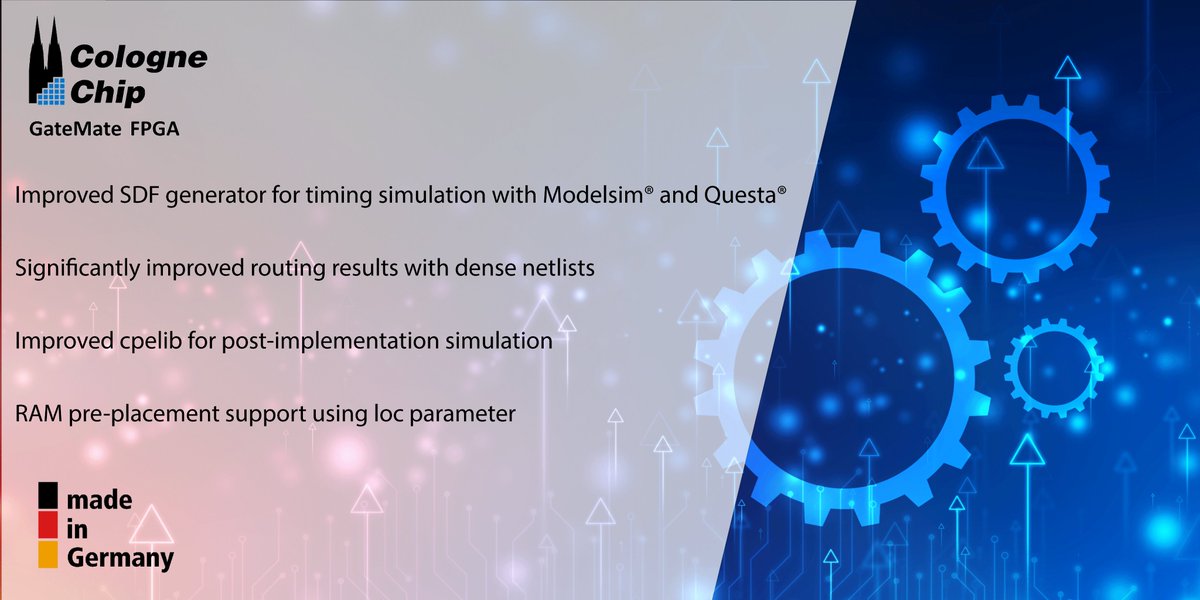

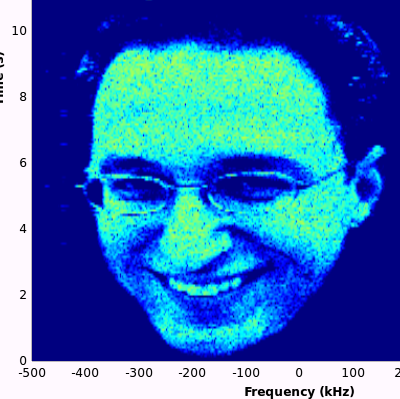

GateMate and Cologne Chip

There are a range of boutique companies developing FPGAs aimed at addressing low to medium-density devices. Cologne Chip is a German company which traces its roots back to 1994 when its predecessor was established to create ISDN ASICs. Nearly 30 years later, Cologne Chip now provides telecommunication ICs, IP and the GateMate FPGA debuting in 2020.

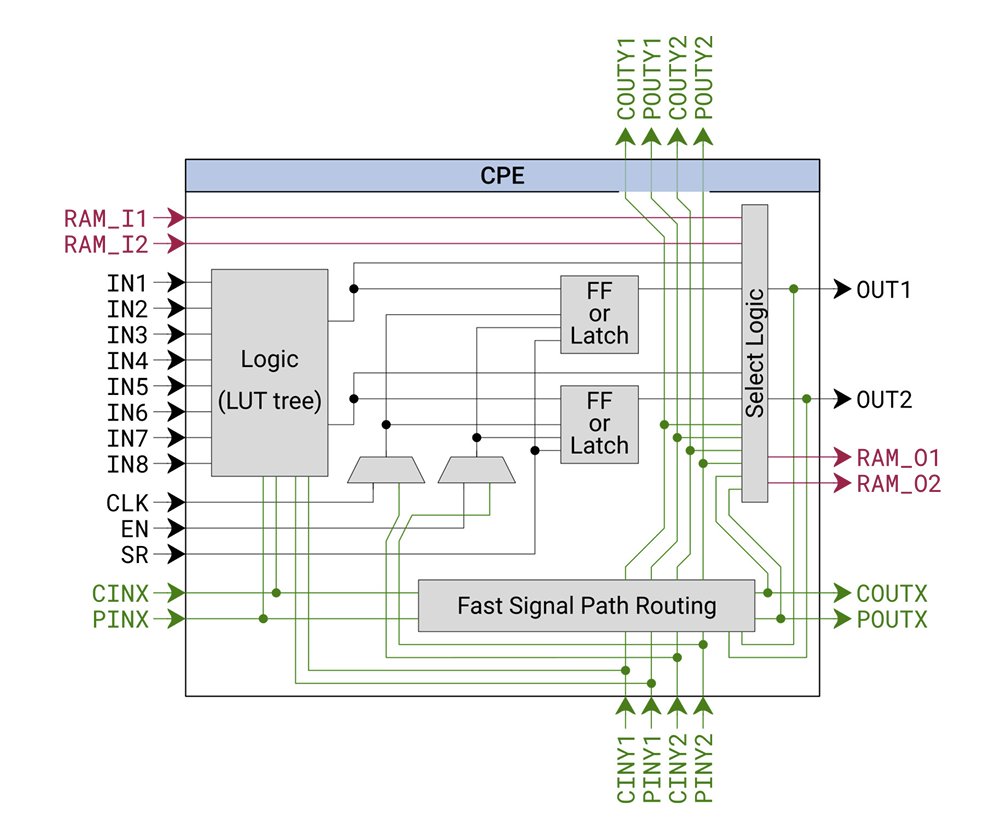

GateMate FPGAs provide between 20,480 (CCGM1A1) and 81,920 (CCGM1A4) Cologne Programmable Elements (CPE).

Each CPE can be configured as either a dual 4-input LUT2 tree, 8-input LUT2, 4-input multiplexor, 1-bit or 2-bit full adder, and 2x2 multiplier. Each CPE also provides developers with two flip flops along with routing.

Since there are two flip flops in each CPE, the number of flip flops available is double the number of available CPEs.

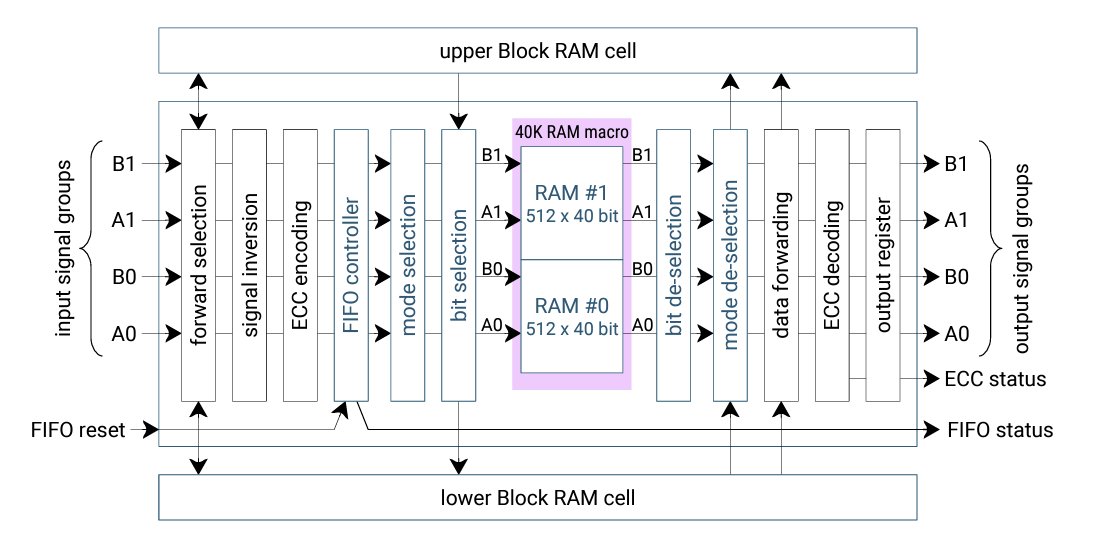

In addition to the programmable logic provided by the CPEs, the GateMate also provides 40 Kb dual-port SRAM BlockRAMs. These BlockRAMS can be configured as either a single 40 Kb memory or two independent 20 Kb elements. Both configurations support true or simple dual-port configurations. To help developers address their application challenges, the BRAMs provide Error Correcting Code and an integrated FIFO controller.

Of course, these RAMS can be cascaded to create larger memories if required.

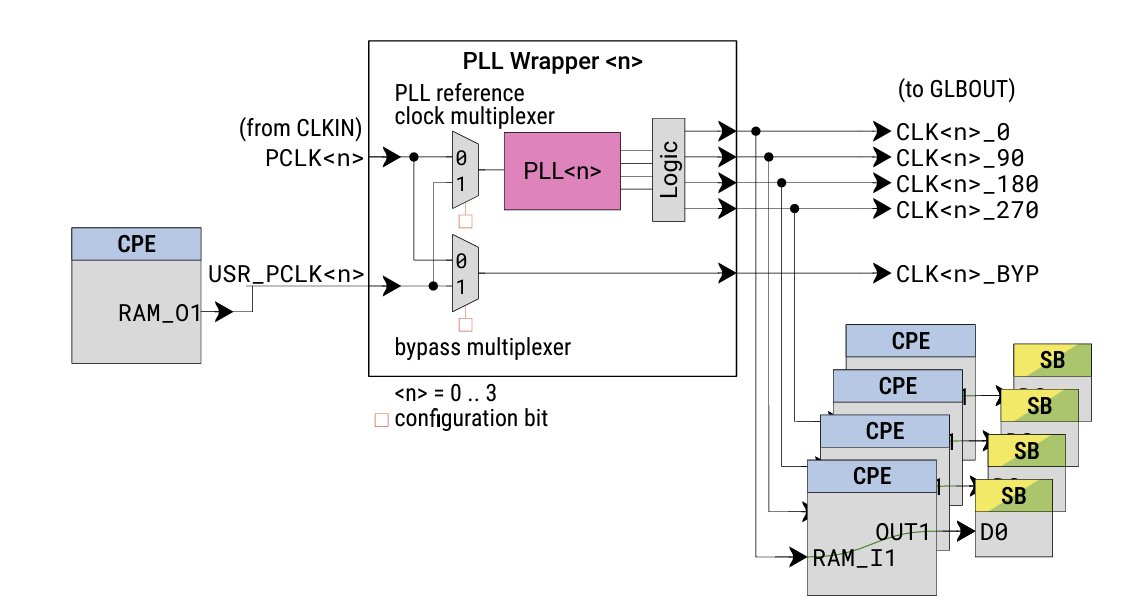

Along with CPE and BRAM resources, modern FPGA designs also have complex clocking requirements. To support more complex clocking requirements, GateMate FPGAs provide users with four PLLs in the smallest available device. These PLL are all digital, which can be driven by either a dedicated clock pin or the device fabric. Each PLL outputs the generated clock frequency, in four-phase shifts of 0, 90, 180, 270.

When it comes to getting signals on and off chip, the GateMate FPGA offers up to 162 single-ended IO or 81 LVDS IO. When in single-ended mode, the GPIO support LVCMOS 1v2, 1v8 and 2v5. The IO cell is interesting because it provides IO flip flops, programmable delay line and Schmitt trigger inputs.

To help get data on and off board at higher data rates, at least one SERDES pair is provided which is capable of operating at up to 2.5 Gbps. As would be expected, larger devices in the series provide more SERDES.

One of the more interesting features of the GateMate FPGA is that the core voltage can be adjusted to optimize for power or performance. Changing between modes is achieved by changing the core voltage supply from 0.9V (low power) to 1v0 (economy) to 1v1 (speed).

GateMate FPGAs are SRAM-based devices which can be configured using either JTAG or SPI and is fabricated on the global foundries 28 nm super low power process.

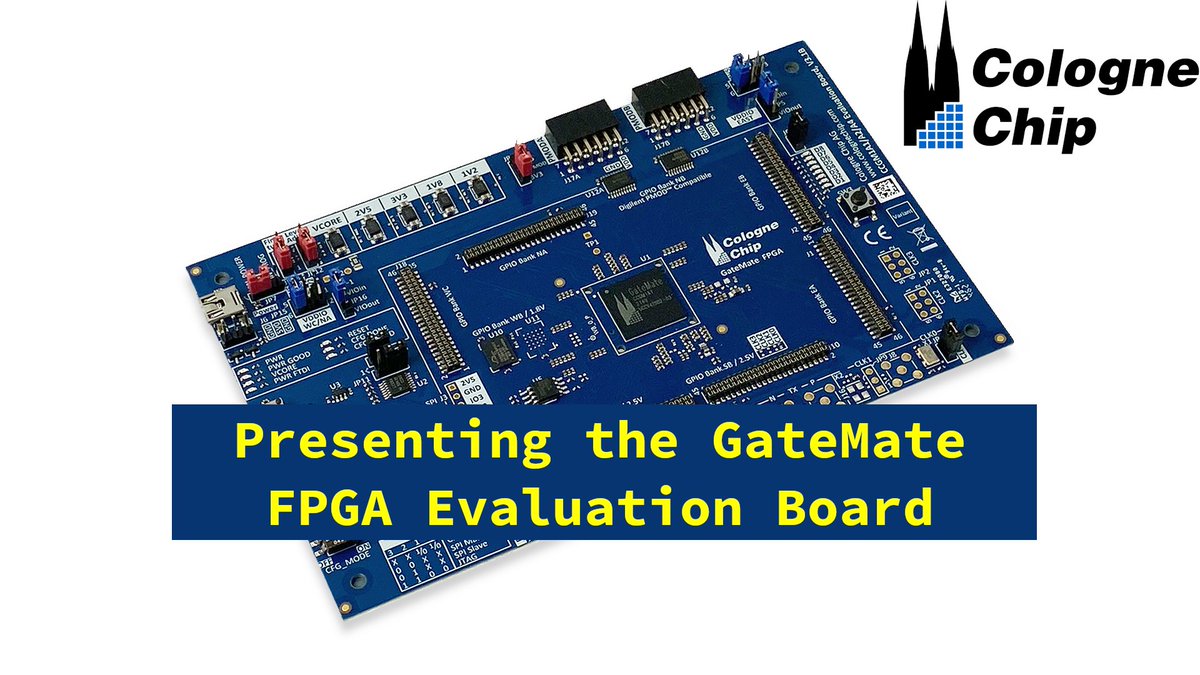

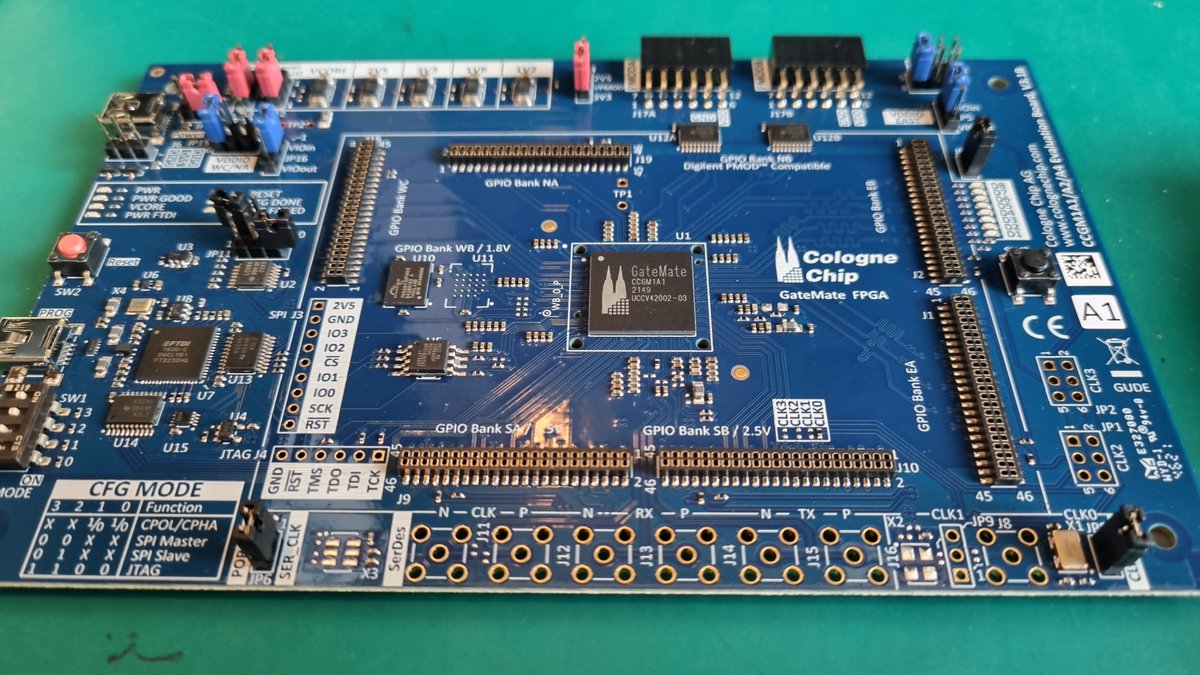

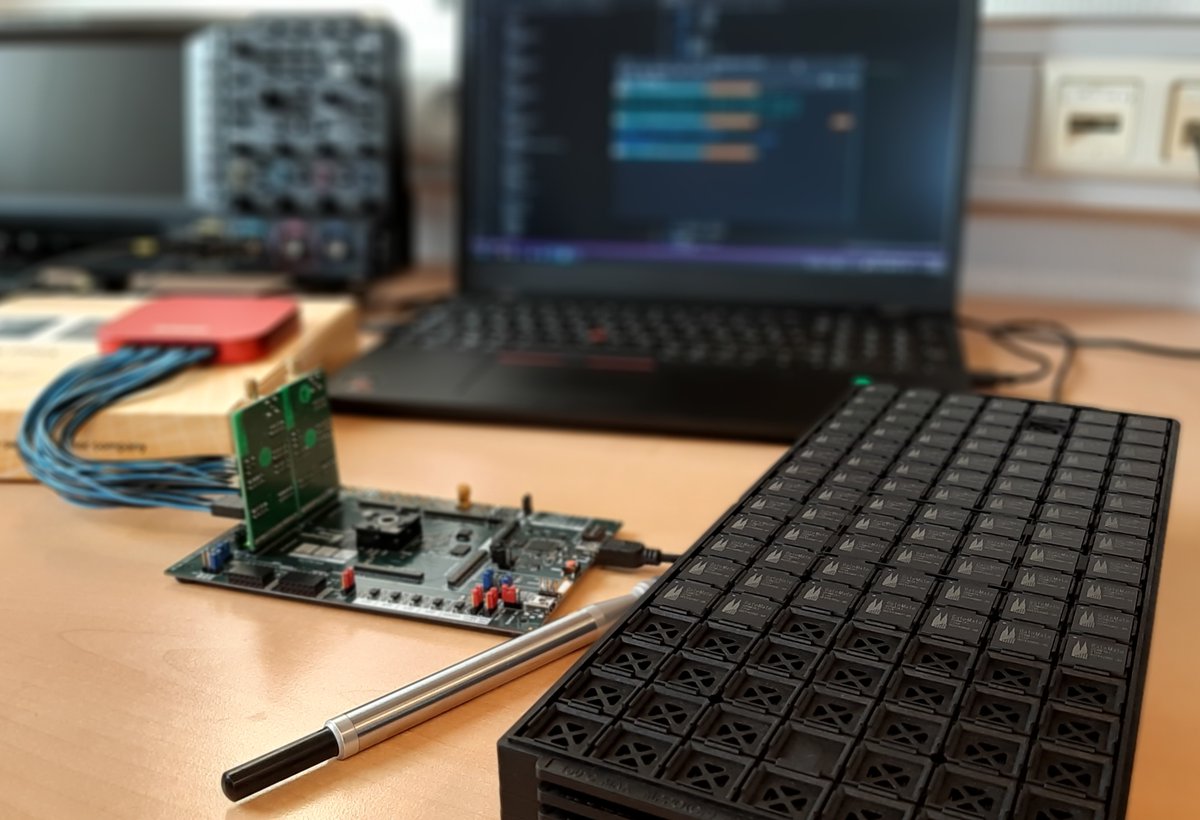

I purchased a GateMate FPGA starter kit to take a closer look at the GateMate FPGA. This starter kit provides a CCGM1A1 device which is the smallest of the family and the one I have described in this blog.

The starter kit provides two Pmods, 108 GPIO, 8 LEDs, SMA break out for the SERDES (not populated) and a HyperRAM (S27KS0641).

In the next blog, we will look at the software tool flow for implementing designs on the GateMate and get something implemented on the development board to explore the flow.

English

Cologne Chip AG and TES Electronic Solutions GmbH announce cooperation. The two companies will work together to offer their customers one-stop-shop FPGA solutions for many embedded applications. bit.ly/3pQcfoG

English

We announce that Cologne Chip is part of IPCEI ME/CT with 30 other companies in Germany. This Important Program of Common European interest will strengthen the European Semiconductor industry and our vision for an innovative next generation of FPGAs.

bit.ly/3qHyn52

English

📷

We have just released our University Program to give Students and Researches an easy access to our GateMate FPGA family with outstanding support and open-source development Tools. Please visit colognechip.com/programmable-l…

English

Cologne Chip AG retweetledi

Guess what new OSHW board is cooking at Olimex? CologneMateA1 is 20K CPE and 5Gbps SerDes and Spartan7 like performance, but comes with completely open source toolchain #fpga #colognematea1 #oshw

English

@mad_archer_ @Olimex Hi, at the moment our Place and Route Tool is not Open Source, but we are working hard on the support for nextpnr (Open Source Place and Route)

English

@Olimex Cool! But I think the place and route is not open source:

GateMate (c) Place and Route

Version 4.2 (1 Apr 2023)

All Rights Reserved (c) Cologne Chip AG

English

@splinedrive @machdyne @y__ Hi,

Ja, das können wir machen. Kannst du uns bitte eine email auf info@colognechip.com schicken mit einer kurzer Beschreibung was Sie machen möchten und um welche Stückzahlen wird es gehen? Danke.

Deutsch

@machdyne @y__ @colognechip Hallo, könntet ihr eventuell spezielle Preise anbieten? Es wäre wirklich cool, FPGA-Chips aus dem eigenen Land zu verwenden. @machdyne ist in Deutschland ansässig und produziert für die Open-Source-Community Boards.

Deutsch

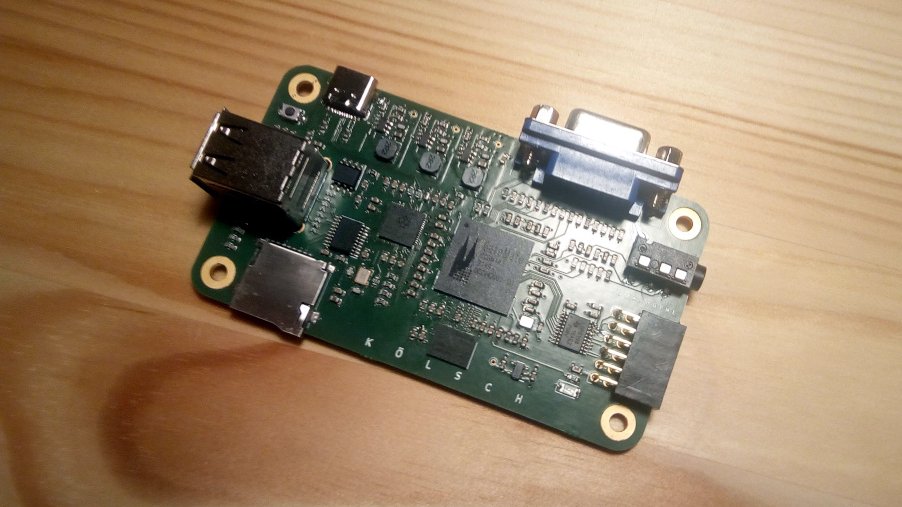

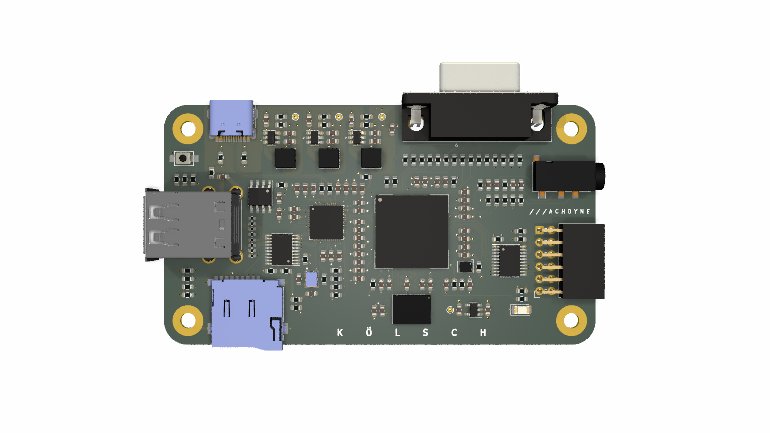

Kölsch is an experimental #FPGA computer based on the #GateMate A1. Coming later this year. machdyne.com/product/kolsch…

English

👉🏻 Interested in evaluating the newest #fpga technology made in Germany?

Have a look at #digikey as one of our latest partners for our #gatemate FPGA-family.

We are happy that shipping has already started 💪🏻

#colognechip #shipping

English

👉🏻📆 We are counting the days! Are you in? We can't wait to show you our innovative #gatemate #fpga from Germany!

🚩Stand# 4A-300 🚩

#colognechip #embeddedworld2022

English

A bit more than a month to go 💪 We are happy to get in personal contact again! Our team is looking forward to meet you at #embeddedworld2022 in Nürnberg! 🚀

#fpga #gatemate #colognechip

Haven't got a ticket yet? 📢 Contact us to get your free ticket:

colognechip.com/about-the-comp…

English

Check out this very readable article - many thanks @BluffJe

fabienm.eu/flf/decouverte…

#gatemate #fpga #flf #colognechip

English

Just finished some final tests: GateMate FPGAs are on their way to assembling the first large batch of evaluation boards!

#CologneChip #GateMate #FPGA

English