william

267 posts

william

@fontamsoc

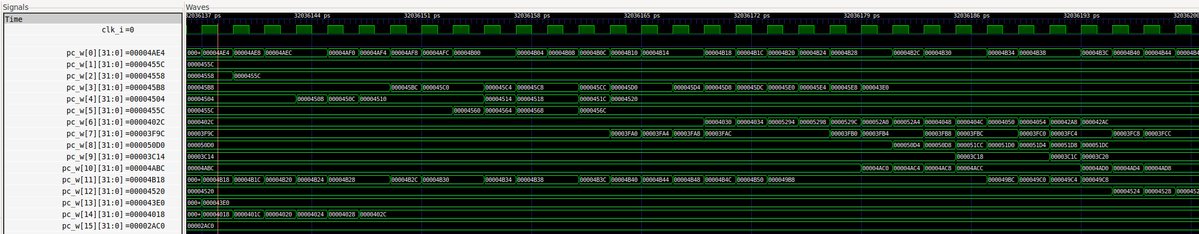

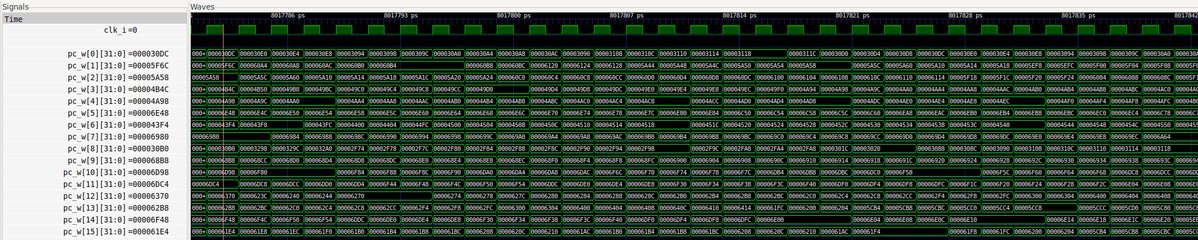

RISC-V RTOS-enabled multi-core SoC using Wishbone4 Interconnect.

Katılım Temmuz 2012

57 Takip Edilen223 Takipçiler

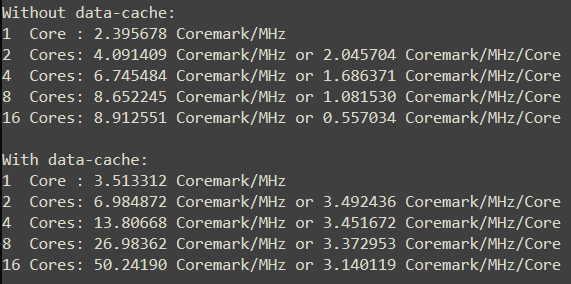

@splinedrive @samsoniuk Hm... IMHO dividing by cores gives you the performance you would get if you use only 1 core out of the multi-cores available.

However we mostly want the performance with all cores involved in the computation.

English

Raw CoreMark is marketing.

CoreMark/MHz/Core is the truth.

@samsoniuk

CoreMark / MHz / Core

Teensy 4.0 (600MHz,1C) 3.86

Metro M4 (200MHz,1C) 2.68

RP2350 DC (276MHz OC,2C) 2.60

RP2350 DC (200MHz OC,2C) 2.60

Metro M4 (180MHz,1C) 2.55

Teensy 3.6 (180MHz,1C) 2.45

Teensy 3.2 (72MHz,1C) 2.34

Teensy 3.2 (96MHz OC,1C) 2.27

Teensy 3.5 (120MHz,1C) 2.21

RP2350 DC (150MHz,2C) 2.00

Metro M4 (120MHz,1C) 1.79

Arduino Zero (48MHz,1C) 1.18

Arduino Due (84MHz,1C) 1.13

ESP32 (240MHz,2C) 0.73

Arduino Mega (16MHz,1C) 0.44

Arduino Nano Every (20MHz,1C) 0.41

adafruit industries@adafruit

RP2350 Dual-Core CoreMark Results: First Numbers Are In! The repository is live, the changes are straightforward, and the benchmarks are now documented directly in the README. If you want to dig in, clone it, tweak clock speeds, or argue about compiler flags, have at it! GitHub repository: github.com/ladyada/CoreMa…

Čeština

@splinedrive I am revisiting which SDRAM controller to use; I have successfully used @ultraembedded SDRAM controller at:

github.com/ultraembedded/…

How does your SDRAM controller compare ?

English

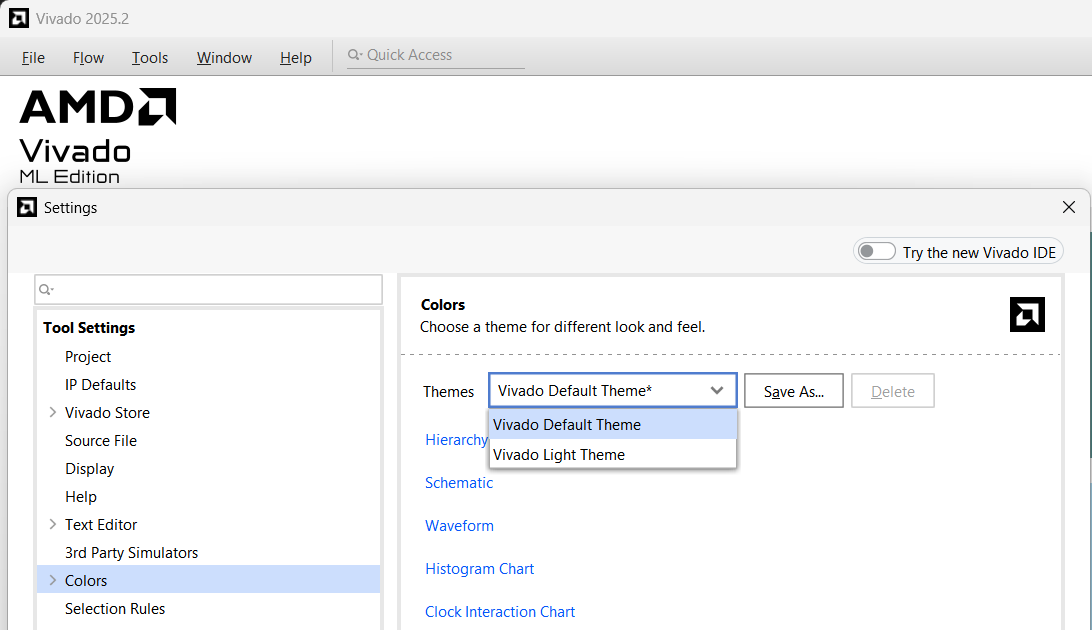

@splinedrive @ATaylorFPGA @samsoniuk Thanks ! Using the new Vivado IDE unlock option for dark theme.

English

@splinedrive @ATaylorFPGA @samsoniuk I installed Vivado 2025.2, but I am only seeing the "Light Theme"; how do I get dark mode ?

English

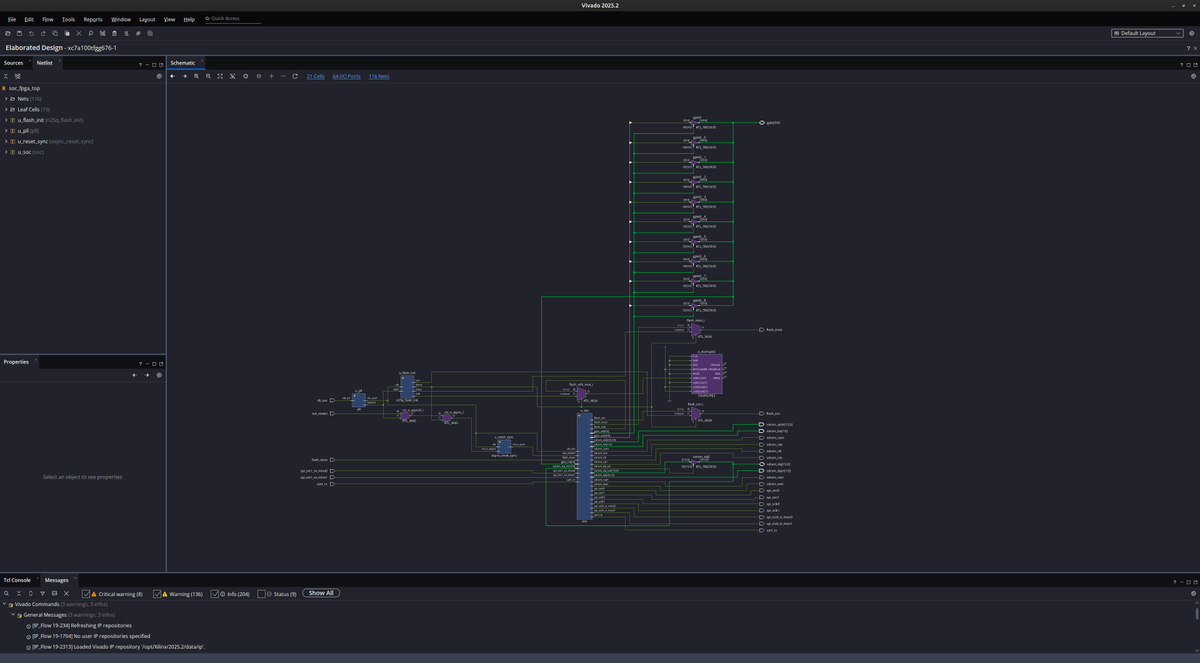

What the hell! Native dark mode, a stylish new Windows layout—look how nice my RTL view of the Linux KianV SoC looks. @ATaylorFPGA @samsoniuk

English

@splinedrive I wish you would look into adding Baremetal RTOS capability using my _OS (underLineOS) approach (ie: in LibC), that is in my opinion simpler than FreeRTOS or Zephyr.

Most Baremetal projects are just looking to use multi-threading along with sw-timer, mutex, semaphore and fifo.

English

@enjoy_digital Is there a guide on how to use LiteScope standalone in a Verilog design ?

English