Sabitlenmiş Tweet

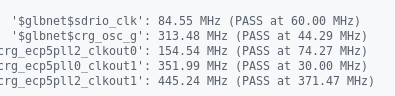

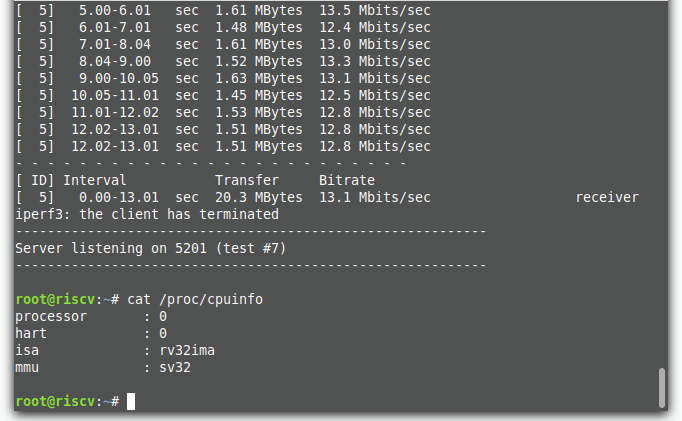

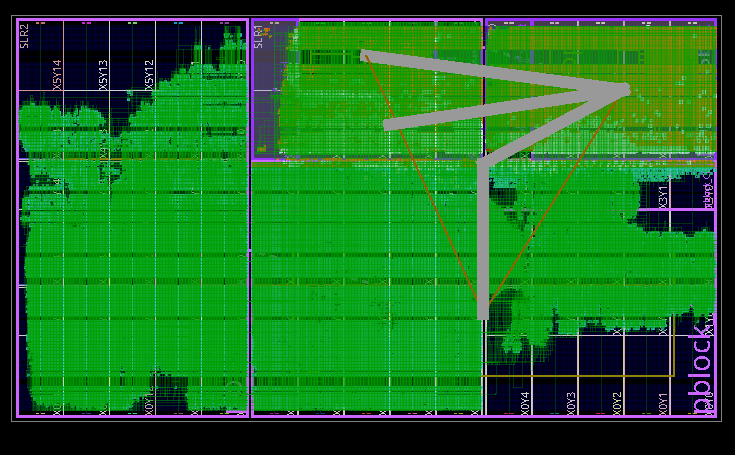

I think I've built myself an HD (720p50) video player out of an #FPGA, #RISCV, #MJPEG and 27,000 lines of Verilog! Going from 800x600 -> 1280x720 just worked with 10 more MHz! I actually plan to sit down and watch a movie on this one evening! github.com/ultraembedded/…

English