پن کیا گیا ٹویٹ

I've received a lot of questions about my various open source projects, status of them, etc.

Made a public google doc with everything:

#gid=0" target="_blank" rel="nofollow noopener">docs.google.com/spreadsheets/d…

English

Andrew Zonenberg @[email protected]

34K posts

@azonenberg

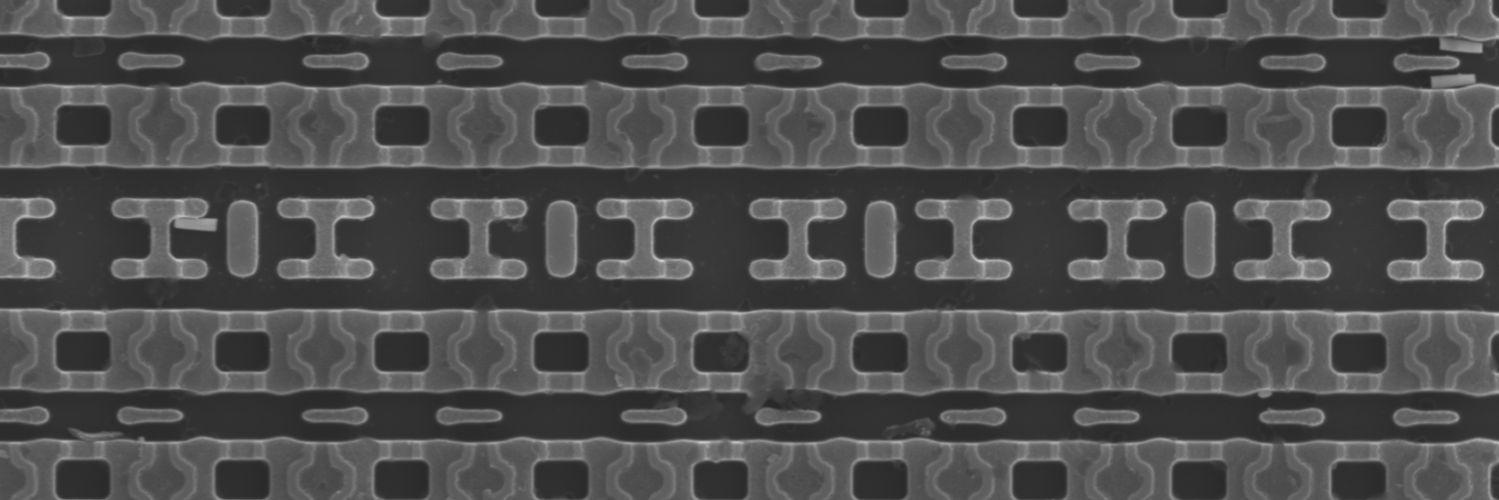

Infosec, RE, high speed digital, T&M, network hardware, microscopy, FPGA/ASIC, @IOActive, KD2HKV, #SoOthersMayLive. Lead dev of glscopeclient. Tweets are my own